Analog IP for GLOBALFOUNDRIES

Welcome to the ultimate

Analog IP

for

GLOBALFOUNDRIES

hub! Explore our vast directory of

Analog IP

for

GLOBALFOUNDRIES

All offers in

Analog IP

for

GLOBALFOUNDRIES

Filter

Compare

794

Analog IP

for

GLOBALFOUNDRIES

from

30

vendors

(1

-

10)

-

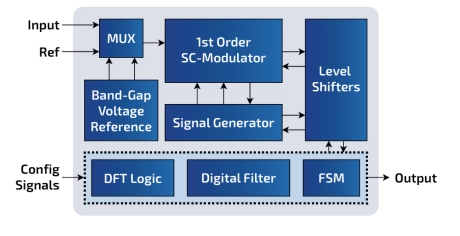

Voltage and Temperature Sensor with integrated ADC - GlobalFoundries® 22FDX®

- Voltage and temperature monitoring

- 3 single-ended voltage measurement inputs

- Operating temperature range: -40°C to 150°C

- Temperature measurement with accuracy up to 1°K ± 1°K change in temperature

-

Crystal Oscillator for a 32 kHz Crystal - GLOBALFOUNDRIES® 22FDX®

- Specific crystal: 32 kHz

- Supported series resistance: up to 100 kOhm

- Supported load capacitance: 3 pF to 12.5 pF

- Startup time: 59 ms (TT, 12 pF) depending on crystal and PCB

-

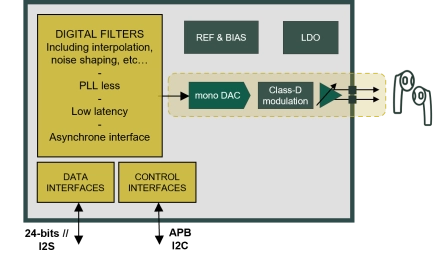

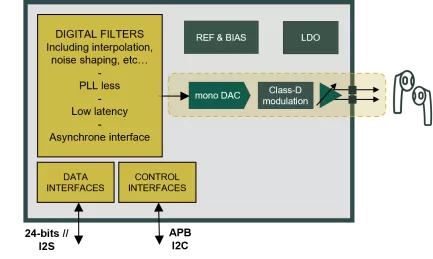

24-bit audio inductor-less class-D DAC with efficiency and ultra-low latency capability in GF 22FDX+

- mDAC115-CDA1-D.01 is a mixed (analog and digital) Class-D Audio DAC in GF 22FDX+ dedicated to head-phone market featuring high efficiency performance.

-

24-bit audio inductor-less class-D DAC with efficiency and ultra-low latency capability

- Provide a top-tier performances audio DAC to fabless and IC companies willing to integrate audio features directly in their product and not using external IC

- High energy efficiency, ow power consumption,

- Ultra low latency for Active Noise Cancellation

- Embedded low noise voltage regulator for best resilience to power supply noise

-

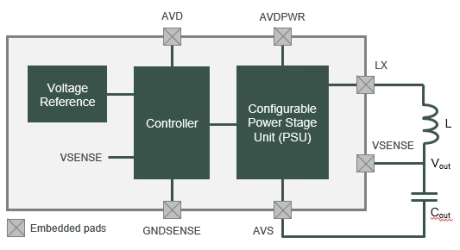

Audio-Grade DC/DC Buck Converter in GF 22FDX

- DCDC-ADG-1.62-5.5-0.5-3.3-A01-G22FDX+_GF_22_FDX+ is an Audio Grade DC/DC Buck Converter in GF 22FDX+ aimed at supplying battery-powered audio IPs.

-

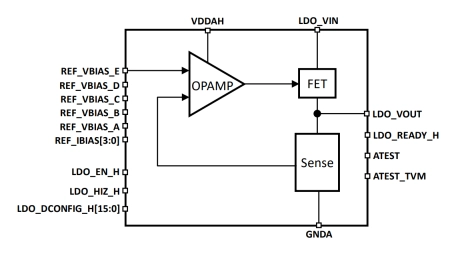

Low Dropout (LDO) Capless Regulator - GF 22FDX

- The ODT-LDO-IC-250M-GF22FDX is a low dropout (LDO), linear regulator for integration in a SoC.

- The LDO uses advanced control techniques to achieve excellent transient response, excellent PSRR performance and low noise.

-

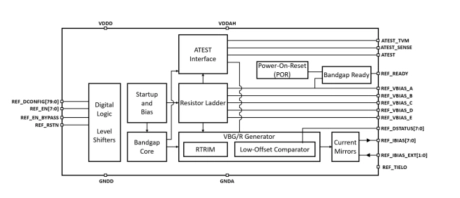

High-performance reference current and voltage generator in GF 22 FDX

- The ODT-REF-GF22FDX-SV1P8 is a highperformance reference current and voltage generator.

- The block incorporates a proprietary architecture to achieve high power supply rejection across an ultra-wide bandwidth, which is needed for high-speed data converter applications.

-

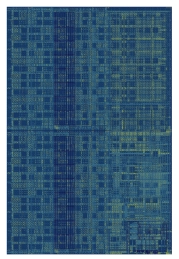

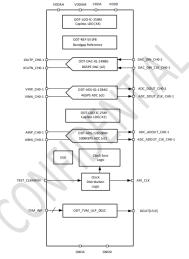

Ultra Low-Power High-Performance AFE on GF 22FDX

- The ODT-AFE-2T2R-GF22FDX is an ultra-highperformance AFE designed in a Global Foundries 22nm process.

- The AFE includes two 12-bit, 4GSPS I/Q ADC pairs, two 14-bit, 8GSPS I/Q DAC pairs, four capless LDOs, one Bandgap reference and one temperature sensor and includes an integrated 3rd party PLL.

-

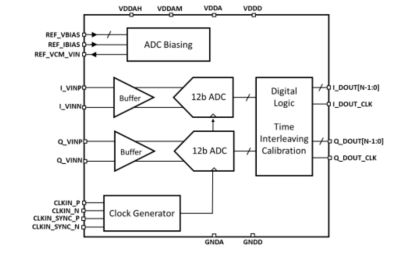

12-bit, 4 GSPS High Performance IQ ADC in GF22FDX

- GF22FDX Process

- 12-bit resolution, 4GSPS update rate

- Dual ADC configured as IQ Pair

-

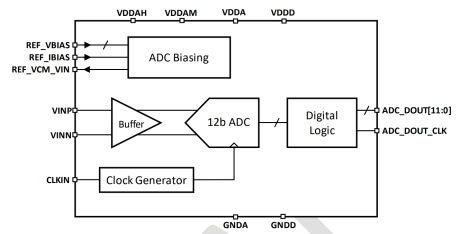

12 bit, 500 MSPS ADC on GF 22FDX

- The ODT-ADS-12B500M-G22FDX is an ultra-low power ADC designed in a 22nm CMOS process.

- This 12-bit, 500MSPS ADC supports input signals up to 100MHz and features a differential full-scale range of 0.8Vpp and excellent static and dynamic performance.

- The ADC architecture is optimized to maximize performance while minimizing power and area consumption. The ADC includes an integrated input buffer.