The APS29 from Cortus provides a solution to your performance challenges while staying within stringent power and silicon footprint budgets. A dual issue pipeline gives performance close to a dual core system with only a modest increase in silicon area and power consumption over a similar single issue core. A static branch predictor dramatically improves the performance of loops and the multiply-accumulate feature increases signal processing speeds. These features offer a significant performance boost but require no special programming techniques.

The APS29 is a very high performance, extendible 32 bit microcontroller core featuring a dual issue pipeline ensuring very high integer throughput. The dual issue pipeline provides instruction level parallelism and increases performance without any requirements to change coding styles or complex compilation schemes. All the performance increases are managed within the processor core and require no effort from the programmer.

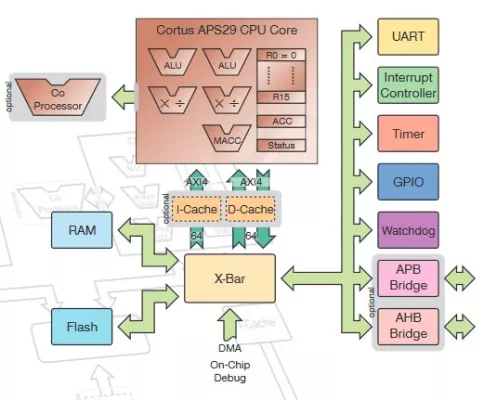

The dual functional units contain a single cycle ALU and multiplier/divider each, and there is one multiply-accumulate unit with a 64 bit accumulator. The load/store unit can coalesce reads and writes onto the 64 bit data bus.

Very High Performance Embedded Microcontroller with Dual Issue Pipeline

Overview

Key Features

- Dual Issue, 5-7 Stage Pipeline

- Multiply - Accumulate

- 2 High Performance Integer Multipliers

- 2 Integer Dividers

- Dual & Multi-Core Capable

- Co-Processor Interface

- AXI4 buses with 64 bit data width

- Coalesced reads/writes

- Optional Caches

Benefits

- A dual issue pipeline gives performance close to a dual core system with only a modest increase in silicon area and power consumption over a similar single issue core.

- A static branch predictor dramatically improves the performance of loops and the multiply-accumulate feature increases signal processing speeds.

Block Diagram

Applications

- Embedded Control

- Encryption and Decryption

- Wireless and Wireline Communication

- Sensor Fusion

- Machine Vision

- Dual and Multi-core Systems

Deliverables

- Full Verilog Source Code

- Full Toolchain

- Graphical Development Environment

- Debugger

- Standard Peripherals

- Full Documentation

- Complete Integration Guide

- Supplied as Part of a Design Services Contract

Technical Specifications

Short description

Very High Performance Embedded Microcontroller with Dual Issue Pipeline

Vendor

Vendor Name

Foundry, Node

All

Availability

Now

Related IPs

- High-performance microcontroller core with a 12-stage dual-issue out-of-order pipeline and a high performance FPU

- Open-source compact microcontroller core with a 4-stage in-order pipeline for deeply embedded applications

- High Performance Embedded Host NVMe IP Core

- 64-bit RISC-V core with in-order dual issue pipeline based complex for Linux-based systems

- Efficient microcontroller core with a 5-stage in-order pipeline, privilege modes, an MPU, L1 and L2 caches

- Efficient microcontroller core with a 5-stage in-order pipeline, privilege modes, an FPU, an MPU, L1 and L2 caches