ViaSat 66200 SDFEC (Soft Decision Forward Error Correction) is a family of turbo product code (TPC) designed for use in 200 Gbps communications applications. The multi rate SDFEC handles BPSK, QPSK, and 16-QAM modulation formats. With either 7% or 20% overhead, TPCs are the optimum FEC for high data rate, high coding gain applications where low latency and high net equivalent coding gain (NECG) are desired.

TPC’s have large minimum distances leading to a very low error floor, which is desired for 200 Gbps optical network applications. Further, TPCs have low complexity while achieving high performance. The 66200 series of cores are based on a soft decision TPC code that ViaSat has used extensively for a variety of applications; hence the architecture is well tested in both simulations and hardware.

The NECG of 20% overhead TPC code is 11.3 dB for coherent QPSK modulation in an AWGN channel at 1x10-15 BER. The 7% overhead TPC code has an NECG of 10.2 dB. Asymptotic analysis reveals that the error floor is more than five orders of magnitude below the 1x10-15 BER performance target.

Soft Decision FEC for 200G Optical

Overview

Key Features

- Baud Rate: ~32 GBaud

- Modulation Configurability - Switchable between:

- PM-BPSK

- PM-DBPSK

- PM-QPSK

- PM-DQPSK

- PM-16QAM

- PM=D16QAM

- Line Rates: ~64 Gbps, ~128 Gbps and ~256 Gbps for (D)BPSK, (D)QPSK and (D)16-QAM respectively.

- FEC Overhead: 7.8% and 20.5% configurable

- Differential Encoding: Supports multiple pre-coding methods as well as bypass

- SDFEC Decoder Bypass: Supported for channel BER monitoring

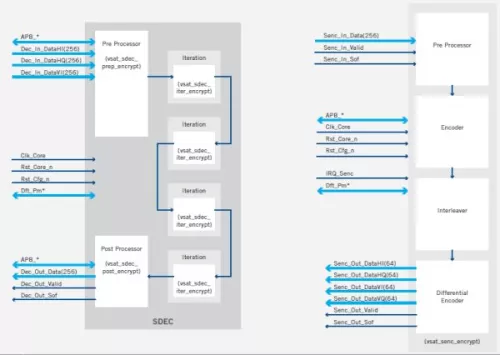

Block Diagram

Technical Specifications

Short description

Soft Decision FEC for 200G Optical

Vendor

Vendor Name

Related IPs

- Soft Decision FEC Encoder/Decoder for 100G Optical

- Multi-constellation and Multi-frequency Correlators Soft GNSS IP for high sensitivity and high accuracy GNSS receivers

- Soft-Decision FEC Integrated Block

- ARC4 Core for Xilinx FPG

- APB Fundamental Peripheral IP, Serial Interface controller for multiple frame formats, SSP (by TI), SPI (by Motorola), Microwire (by NS), I2S (by Philips), AC - link (by Intel) and SPDIF (by Intel), Soft IP

- APB Fundamental Peripheral IP, I2C controller, Soft IP