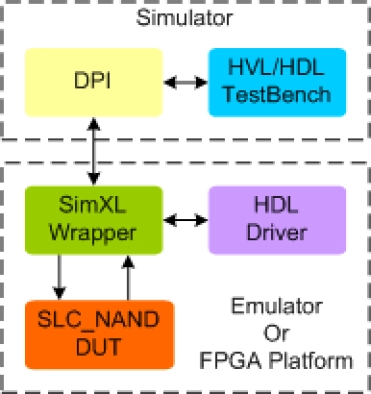

SLC NAND Synthesizable Transactor provides a smart way to verify the SLC NAND component of a SOC or a ASIC in Emulator or FPGA platform. The SmartDV's SLC NAND Synthesizable Transactor is fully compliant with standard SLC NAND Specification and provides the following features.

SLC NAND Synthesizable Transactor

Overview

Key Features

- Supports 100% of SLC NAND protocol standard

- Supports all the SLC NAND commands as per the specs

- Provides cost effective solutions for mass storage applications

- Supports the following devices:

- 8

- 16

- Supports multiplexed address/data

- Supports page size of (512 + 16 spare) bytes for x8 device

- Supports page size of (256 + 8 spare) words for x16 device

- Supports block size of (16k + 512 spare) bytes for x8 device

- Supports block size of (8k + 256 spare) words for x16 device

- Supports page read/program

- Supports copy back program mode for fast page copy without external buffering

- Supports fast block erase time of 2ms

- Supports status register

- Supports electronic signature

- Supports chip enable don’t care

- Supports hardware data protection

- Supports Data integrity of 100,000 program/erase cycles

- Models, detects and notifies the test bench of significant events such as transactions, warnings, timing and protocol violations

Benefits

- Compatible with testbench writing using SmartDV's VIP

- All UVM sequences/testcases written with VIP can be reused

- Runs in every major emulators environment

- Runs in custom FPGA platforms

Block Diagram

Deliverables

- Synthesizable transactors

- Complete regression suite containing all the SLC NAND testcases

- Examples showing how to connect various components, and usage of Synthesizable Transactor

- Detailed documentation of all DPI, class, task and function's used in verification env

- Documentation contains User's Guide and Release notes

Technical Specifications

Short description

SLC NAND Synthesizable Transactor

Vendor

Vendor Name