NAND Flash Synthesizable Transactor provides a smart way to verify the NAND Flash component of a SOC or a ASIC in Emulator or FPGA platform. The SmartDV's NAND Flash Synthesizable Transactor is fully compliant with standard HY27UH08AG(5/D)M Specification and provides the following features.

NAND Flash Synthesizable Transactor

Overview

Key Features

- Supports 100% of NAND Flash protocol standard of HY27UH08AG(5/D)M

- Supports all the NAND Flash commands as per the specs

- Supports NAND interface of x8 width

- Supports multiplexed address/data

- Supports memory cell array of (2K+64) bytes *64 pages*16,384 blocks

- Supports page size of (2K + 64 spare) bytes for x8 device

- Supports block size of (128K + 4K spare) bytes for x8 device

- Supports page read/program

- Supports copy back program mode for fast page copy without external buffering

- Supports cache program mode to improve the program throughput

- Supports fast block erase time of 2ms

- Supports status register

- Supports electronic signature

- Supports chip enable don’t care

- Supports hardware data protection

- Provides cost effective solutions for mass storage applications

- Models, detects and notifies the test bench of significant events such as transactions, warnings, timing and protocol violations

- Protocol checker fully compliant with NAND Flash specification HY27UH08AG(5/D)M

Benefits

- Compatible with testbench writing using SmartDV's VIP

- All UVM sequences/testcases written with VIP can be reused

- Runs in every major emulators environment

- Runs in custom FPGA platforms

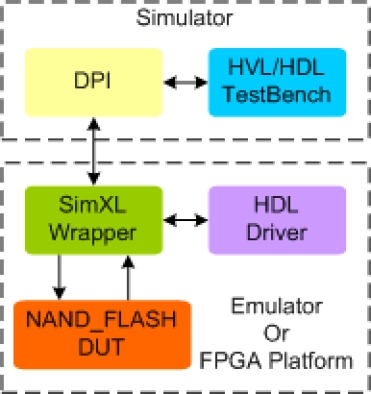

Block Diagram

Deliverables

- Synthesizable transactors

- Complete regression suite containing all the NAND Flash testcases

- Examples showing how to connect various components, and usage of Synthesizable Transactor

- Detailed documentation of all DPI, class, task and function's used in verification env

- Documentation contains User's Guide and Release notes

Technical Specifications

Short description

NAND Flash Synthesizable Transactor

Vendor

Vendor Name