The SD / SDIO 3.0 Combo Device IP Core is a high performance controller capable of interfacing with memory cards and I/O applications such as WLAN, Bluetooth, etc up to a peak banswidth of 832 Mbps (UHS-I). This IP is compliant with the latest SD, SDIO standard and supports asynchronous interrupts to improve card performance.

SD 3.0 / SDIO 3.0 Combo Device Controller

Overview

Key Features

- Meets SD Memory Card Physical Layer Specification version 3.0

- Meets SDIO card specification ver 3.0

- Host clock rate variable between 0 and 208 MHz

- All SD bus modes supported including SPI, 1 and 4 bit SD.

- Asynchronous interrupt to host for improved performance

- Upto 832Mbits per second read and write rates using 4 parallel data lines

- Programmable through a standard AMBA AHB interface

- Supports Suspend/Resume functions to optimize multi-function cards

Benefits

- RMM-compliant synthesizable RTL design in Verilog

- Easy-to-use test environment

- Synthesis scripts

- Technical documents

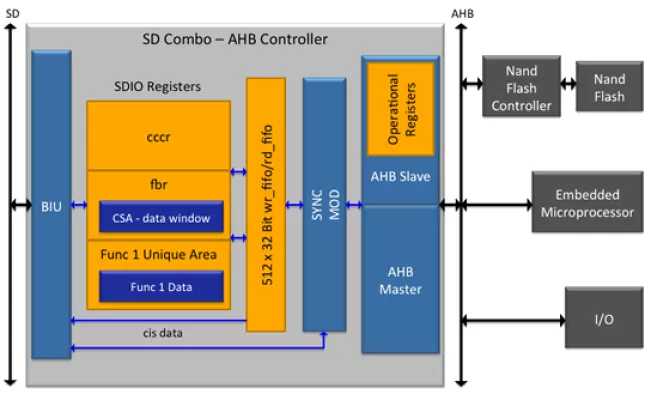

Block Diagram

Deliverables

- RMM complaint Verilog RTL

- Synthesis scripts

- Test environment

- Technical documentation

Technical Specifications

Availability

Now