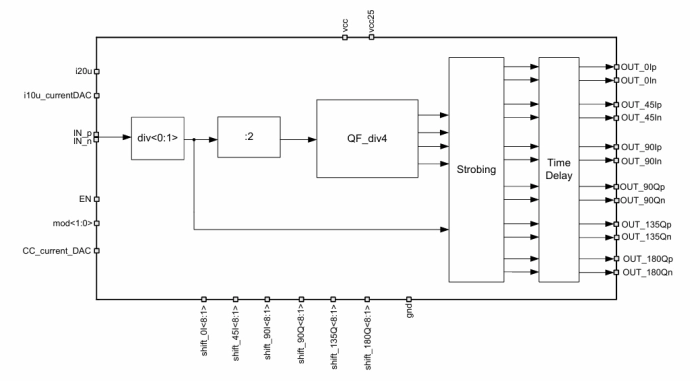

This device is designed to generate a quadrature heterodyne (oscillator) signal. CML logic quadrature generator consists of pre-switchable divider with the division factor 1, 2, 4, 8, divider by 2, divider by 4 that form quadrature signal, output signal (to the input) strobbing block, and phase adjustment block implemented on signal delay time.

Quadrature former 75-750 MHz

Overview

Key Features

- TSMC CMOS 65 nm

- Output frequency range 75-750 MHz

- Input signal division (by 8, 16, 32 or 64)

- High accuracy of the phase control

- Operating-temperature range: from -40 °C to + 125 °C

Block Diagram

Applications

- Quadrature signal processing for mixer

Deliverables

- Schematic or NetList

- Abstract model (.lef and .lib files)

- Layout view (optional)

- Behavioral model (Verilog)

- Extracted view (optional)

- GDSII

- DRC, LVS, antenna report

- Test bench with saved configurations (optional)

- Documentation

Technical Specifications

Short description

Quadrature former 75-750 MHz

Vendor

Vendor Name

Foundry, Node

TSMC CMOS 65 nm

Maturity

Silicon proven

Availability

Now

TSMC

Silicon Proven:

65nm

G