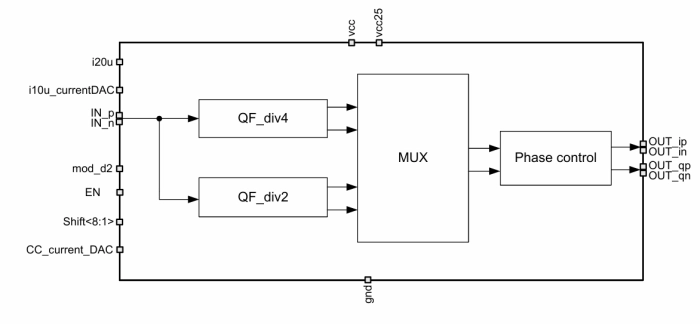

The quadrature former with phase correction. Quadrature signal is formed in the trigger cell by means of division by 2.

D-trigger synchronize output signal with input signal to minimize phase error.

The QF is designed using TSMC 65 nm CRN65LP technology.

0.75-1.20 GHz quadrature former

Overview

Key Features

- TSMC CMOS 65 nm

- Output frequency range 0.75-1.20 GHz

- Input signal division by 2

- 0.1 degree precise phase adjustment

- Strobing of output signal

Block Diagram

Applications

- Quadrature signal processing for mixer

Deliverables

- Schematic or NetList

- Abstract model (.lef and .lib files)

- Layout view (optional)

- Behavioral model (Verilog)

- Extracted view (optional)

- GDSII

- DRC, LVS, antenna report

- Test bench with saved configurations (optional)

- Documentation

Technical Specifications

Short description

0.75-1.20 GHz quadrature former

Vendor

Vendor Name

Foundry, Node

TSMC CMOS 65 nm

Maturity

silicon proven

Availability

Now

TSMC

Silicon Proven:

65nm

G