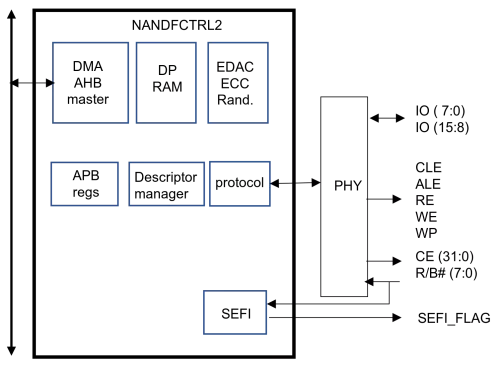

NANDFCTRL2 is a VHDL IP core implementing an interface to NAND flash memory devices. The core supports ONFI 4.0 and provides DMA transfers to and from the memory. The core implements a BCH EDAC with capability of correcting 60 errors per chunks of 1024 bytes of data. The actual error correction capability is configured by means of VHDL generics, in conjunction with the configuration of memory support. The EDAC can be combined with a data randomizer, which breaks any repetetive bit patterns, thereby increasing memory endurance. Both the EDAC and the Randomizer can be bypassed during runtime if the user needs to access the memory without them.

To support detection and recovery from SEFI, the core provides timeout functions in addtion to the EDAC. The SEFI detection functionality monitors ongoing accesses towards the flash to detect if any access is too long, which could indicate an error in the memory.

For details about the actual flash memory interface, flash memory architecture and ONFI 4.0 command set please refer to the Open NAND Flash Interface specification, revision 4.0.

NAND Flash Memory Controller with DMA

Overview

Key Features

- ONFI 4.0 support

- All mandatory ONFI 4.0 commands

- Asynchronous / SDR data interface timing mode 1-5

- BCH EDAC with up to 60 bits correction capacity per 1024 bytes chunks of data

- Randomization of memory data

- Basic timeout based SEFI detection and reporting

Block Diagram