The silicon-proven MIPI® M-PHY IP, compliant with the latest MIPI M-PHY v5.0 specification, supports speeds up to 23.32 Gbps per lane. The IP is optimized for a broad range of high-speed interfaces for applications including JEDEC Universal Flash Storage (UFS) and UniPro interfaces which are widely used in mobile and automotive applications. The M-PHY IP, ideal for embedded storage and chip-to-chip communication, provides low-power features, fast transitions between high-speed burst to low power saving modes, and the ability to manage the TX and RX directions independently.

The MIPI M-PHY IP supports HS Gear1, Gear2, Gear3, Gear4 and Gear5 rates ranging from 1.248 Gbps to 23.32 Gbps per lane. Low-speed capabilities are available with Gear1 to Gear5 PWM modes. A sophisticated clock recovery mechanism and power-efficient clock circuitry are designed to guarantee the integrity of the clocks and signals needed to meet strict timing requirements. The MIPI M-PHY IP supports large and small amplitudes, slew rate control and dithering functionality for optimized electromagnetic interference (EMI).

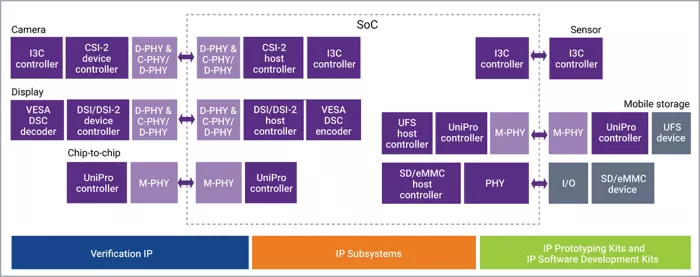

The MIPI M-PHY IP along with the Universal Flash Storage (UFS) Host Controller IP or the MIPI UniPro Controller IP provides a single vendor UFS IP solution that designers can easily integrate into application processors with less risk, while speeding time-to-market of advanced SoCs and device integrated circuits (ICs).