Perceptia’s DeepSub™ pPLL02 is a general purpose all digital PLL featuring low-jitter and compact area suitable for many clocking applications at frequencies up to 2GHz. It is suitable as a clock source for moderate speed microprocessor blocks and other logic.

To give SoC designers the maximum flexibility in building complex multi-domain clock systems, pPLL02F is very small and low power. pPLL02F integrates easily into any SoC design and includes all the views and models required by back end flows.

The pPLL02F is built using Perceptia’s all digital PLL technology. This robust technology delivers identical performance regardless of PVT conditions. It consumes a small fraction of the area of an analog PLL whilst maintaining comparable performance.

Perceptia further provides integration support and offers customization and migration services.

Minimum-area low-power clocking PLL (1st Gen)

Overview

Key Features

- - Super small: 220 x 230 microns!

- - Very low power: 36-mW

- - Broad frequency range: 2-GHz

- - Fast lock

- - Preprogrammed loop filter

- - Scan testable

- - Decoupling caps for lower jitter

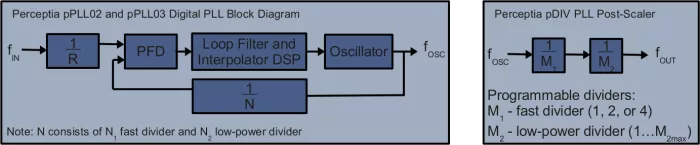

Block Diagram

Technical Specifications

Short description

Minimum-area low-power clocking PLL (1st Gen)

Vendor

Vendor Name

Foundry, Node

180 nm

Availability

Now

Silterra

Silicon Proven:

180nm