The MIPI I3C interface is an evolutionary standard that improves upon the features of I2C, while maintaining backward compatibility. This standard offers a flexible multi-drop interface between the host processor and peripheral sensors to support the growing usage of sensors in embedded systems.

The main purpose of MIPI I3C is threefold:

To standardize sensor communication

Reduce the number of physical pins used in sensor system integration and

Support low-power, high-speed and other critical features that are currently covered by I2C and SPI.

I3C Host Controller

Overview

Key Features

- Compliant with MIPI I3C Specification V1.0

- Compliant with MIPI I3C HCI Specification V1.0

- Supports up to 12.5 MHz operation using Push-Pull

- Open-Drain and Push-pull type transactions (as required)

- Supports legacy I2C devices

- Dynamic Addressing while supporting Static Addressing for Legacy I2C devices

- Legacy I2C Messaging

- I2C-like Single Data Rate Messaging (SDR)

- Optional High Data Rate Messaging Modes (HDR)

- Support for Multi-host (transferring the ownership of the bus to a Secondary Host if Present)

- Reception of In-band Interrupt Support from the I3C Slave devices

- Reception of Hot-Join from newly added I3C Slave devices

- Synchronous Timing Support and Asynchronous Time Stamping.

- APB/AHB Target Interface for Configuring/Controlling the IP with Interrupt output

- Small 16-byte (Configurable) FIFO for transferring data between Host and the Device

- Independent Clocks for AHB and the I3C Interface

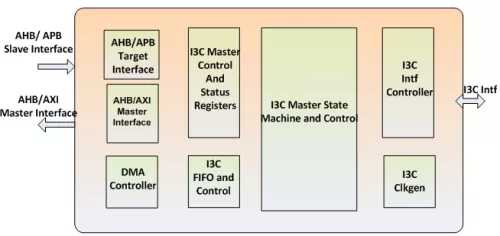

Block Diagram

Deliverables

- RMM compliant synthesizable RTL design in Verilog

- Easy-to-use test environment

- Synthesis scripts

- Technical documents

- Validated with 3rd Party UVM-based Slave VIP and available as an additional option

Technical Specifications

Maturity

Silicon proven

Availability

NOW

Related IPs

- MIPI I3C Controller Host/Target IP

- MIPI I3C Basic v1.1.1 specifications with Host Controller Interface v1.1 specification

- USB 3.2 Host Controller

- I3C V1.1 Advanced Controller

- I3C Advanced Controller Lite

- I3C Controller IP – I3C / I2C Slave, SCL Clock only, Configure User Registers, no CPU Host Required