ND1000 JPEG CODEC is a high-performance and low-area cost JPEG encoder/decoder, which performs interconverting between JPEG standard compatible stream and image raster data as encoder or decoder. The standard file format(JEIF etc.) formats are supported.

ND1000 can be integrated to SOC as hardware JPEG encode/decode accerlerator and also can be used as co-processor in various image processing systems to realize low-bandwidth and high-performance image processing.

High Performance 8bit/12bit JPEG CODEC

Overview

Key Features

- Performance

- 480M pixels per second @400Mhz, YCbCr420

- Running Mode

- Stand-alone mode (memory to memory)

- Peripheral mode (FIFO interface)

- JPEG Profile

- Baseline process

- Extended sequential DCT-base process (sequential)

- Image Size

- Resolution up to 32768 x 32768 pixels

- Min size: 1 MCU

- Min step size: 4 pixels

- Color Depth

- 8-bit/12-bit

- Image source data format

- YCbCr 420, planar/ semi planar, 8-bit/12-bit

- YCbCr 411, planar/ semi planar, 8-bit/12-bit

- YCbCr 440, planar/ semi planar, 8-bit/12-bit

- YCbCr 422, planar/ semi planar, 8-bit/12-bit

- YCbCr 444, planar/ semi planar, 8-bit/12-bit

- YUV 422-interleaved, UYVY, YUYV, 8-bit/12-bit

- XRGB32/RGB24/RGB565 (Support down-sampling to YCbCr422/YCbCr420 when encoding)

- 4 components format, 8-bit/12-bit

- Encoding/Decoding

- Encoder/Decoder software configurable

- Support single component (Y/Cb/Cr) non-interleaved scanning

- ROI: Region of Image encoding/decoding

- RST: Restart interval encoding/decoding

- Support stream multi-buffering

- Support slice encoding/decoding

- Quantization table and Huffman table auto fetch

- Decoding error interrupt: run-length error, RST marker error

- System Interface

- AXI-3 Data Bus

- AHB Configuration Bus

- Common FIFO interface

Benefits

- Custom design for JPEG CODEC is available.

- High Performance both Decoding and Encoding.

- Multi-format data source for Encoder.

- Multi-format output format for Decoder.

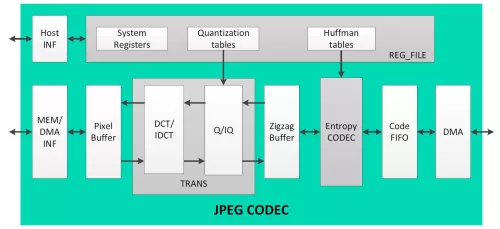

Block Diagram

Applications

- Digital Camera

- Mobile Phones

- Video Systems

- Scanners and Printers

Deliverables

- Fully verified synthesizable RTL source code

- RTL test bench

- Datasheet/Integration Guide

- Verification Guide

Technical Specifications

Short description

High Performance 8bit/12bit JPEG CODEC

Vendor

Vendor Name

Availability

Immediately

Related IPs

- ColdFire V2 IP Core low-gate count, high performance ColdFire architecture

- 8-bit Baseline JPEG Codec with Optional Video Rate Control

- High Performance Embedded Host NVMe IP Core

- High Speed Low Power JPEG Codec IP Core

- JPEG Codec 4K(YUV422) 96fps@200MHz,

- Lossless JPEG Codec Full HD(YUV422) 24fps@100MHz. (1Sample/clk)