The APS3R is a fully 32 bit general purpose CPU designed specifically to meet the needs of embedded systems.

The APS3R is a 32 bit core with 4 GB address space and a Havard architecture. The instructions are 16 bits in length, with a 16 bit extension when needed (no mode switches necessary) giving excellent code density. The pipeline features out-of-order execution enabling nearly all instructions to execute in a single cycle, including loads and stores. Interrupts are fully vectored and the architecture ensures a minimum of software overhead in task switches. The processor was designed to execute high level languages, notably C, with ease. The software application can be entirely realised in C, interrupt routines included. The entire GNU GCC toolsuite has been ported to this architecture.

Energy efficient, small footprint, 32 bit microcontroller core

Overview

Key Features

- Energy Efficient RISC Core

- Harvard architecture

- 2.76 DMIPS/MHz

- 3-stage pipeline

- Low Power

- Good Code Density

- High Clock Frequency (> 300MHz in 90nm)

- Integer Multiplier (sequential or parallel)

- Up to 250 Low Latency Vectored Interrupts

- Dual-core Capable

Benefits

- Good performance CPU

- Tiny silicon footprint, less slicon area

- Low Power, longer battery life

- Good Code Density, less Flash memory required

- High maximum clock frequency, more performance, more time sleeping

- Dual-Core Capable, more performance without exploding consumption

- RTOS support: FreeRTOS, uCLinux, uC/OS II, uC/OSIII, TargetOS

- Full Development Environment

- Optional standard peripherals (counter, timers, watchdog, GPIO, I2C, SPI & UARTs)

- Optional Ethernet 10/100 MAC and USB2.0 Peripheral

- Optional JTAG-Ethernet Debug Solution

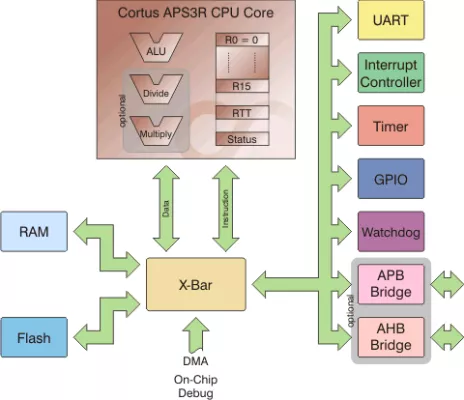

Block Diagram

Applications

- Wireless e.g. Bluetooth or Bluetooth LE

- Smart metering

- Security applications

- Internet of Things (IoT)

- Touchscreen controllers for smartphones and tablets

- Smart cards

Deliverables

- Full Verilog Source Code

- Full Toolchain

- Graphical Development Environment

- Debugger

- Standard Peripherals

- Full Documentation

- Complete Integration Guide

- Supplied as Part of a Design Services Contract

Technical Specifications

Short description

Energy efficient, small footprint, 32 bit microcontroller core

Vendor

Vendor Name

Foundry, Node

All

Maturity

In Full Production

Availability

Now

Related IPs

- Energy efficient, small footprint, excellent code density, 32 bit microcontroller

- High performance, flexible, 32 bit Energy Efficient Embedded Microcontroller

- Energy efficient, low cost, 8 bit replacement, 32 bit microcontroller

- Small, Low Power, Energy Efficient 32-bit Microcontroller Processor

- High performance, flexible, extendible 32 bit microcontroller core featuring excellent code density

- Efficient microcontroller core with a 5-stage in-order pipeline, privilege modes, an MPU, L1 and L2 caches