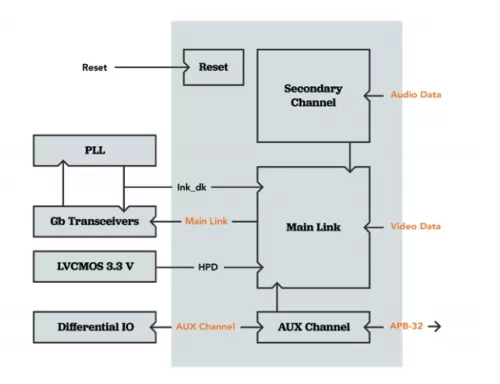

Our 5th generation DisplayPort Transmitter Link Controller core supports DisplayPort 1.4, 2.0 and embedded DisplayPort 1.4b features, including link rates up to 8.1Gbps, Display Stream Compression (DSC 1.2), multi-stream transport (MST) and more. The base core includes all required link functionality—Main Link, Secondary Channel, and AUX Channel protocols—and supports the HDCP 1.3 and HDCP 2.2 standards for data encryption.

The DisplayPort Transmitter core interfaces use common industry standards for low-complexity integration.

DisplayPort Transmitter Link Controller

Overview

Key Features

- Silicon proven on multiple ASIC and FPGA processes with multiple PHY partners.

- 1, 2 or 4 pixels per input cycle, supporting up to 16K resolution input per source

- 1.62-8.1Gbps link rate across 1,2, or 4 lanes

- SST or MST operation

- Full secondary channel support

- Real time HDCP 1.3/2.2/2.3 support

- Optional eDP 1.4b support

- Deep color and HDR support

- DSC transport with Forward Error Correction support

- Interfaces to external PHY. Compatible with 3rd-party PHYs for ASICs from 7nm to 65nm technologies. FPGA targeted implementations are also available.

Block Diagram

Deliverables

- HDL source files for the function design

- HDL source files for block level and top level testing

- Functional specification

- Timing constraints summary document

- Generic SRAM simulation models

- C Reference Driver

- C Link Policy Maker

Technical Specifications

Foundry, Node

65nm, 40nm, 28nm, 14nm

Maturity

In Production

Availability

Immediate