Silicon agnostic implementation of the CPRI 6.1 specification

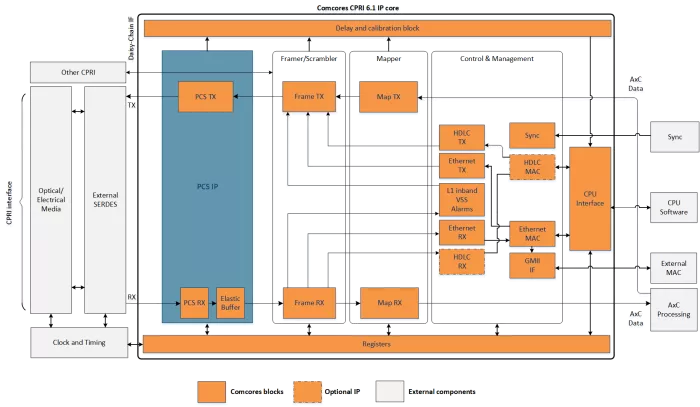

The Common Public Radio Interface (CPRI) 6.1 core is a silicon agnostic implementation of the CPRI 6.1 specification, which is targeting both ASIC and FPGAs. CPRI is a high-speed serial interface designed to meet or exceed the requirements of base band systems, C-RAN switches, Digital Front-End (DFE) processors or advanced test systems. With its extreme flexibility and reduced logic consumption, the CPRI 6.1 IP core is the perfect match whether the application is REC (Radio Equipment Controller) or RE (Radio Equipment).

The core can be dynamically configured to handle wireless multi-mode radio systems implementing deterministic latency features and high-performance throughputs required by LTE-A and 5G radio base stations.

The CPRI cores come in several versions to suit any implementation scenario whether speed, a compact size or a wide feature set is required. Comcores can offer a 64-bit version of the IP core which ensures easy time-closure even at the highest speeds.