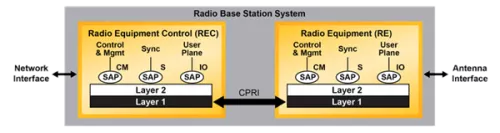

This document provides technical information about the Lattice Common Public Radio Interface (CPRI) IP core. This IP core together with SERDES and Physical Coding Sublayer (PCS) functionality integrated in the LatticeECP3™ and ECP5™ LFE5UM FPGAs implements the physical layer of the CPRI specification and interleaves IQ data with synchronization, control and management information. It can be used to connect Radio Equipment Control (REC) and Radio Equipment (RE) modules.

The CPRI IP core implements not only all of the capabilities required to support the physical layer of the CPRI specification (basic function), but also specific requirements related to link delay accuracy (low latency character).

One CPRI core configuration for 5G version (4.9152 Gbps) is also supported. It is similar to the "low latency" one for 3G version except the data rate.

Common Public Radio Interface - IP Core

Overview

Key Features

- Supports the physical link layer (Layer 1) of the CPRI specification

- Supports three standard bit rates of the CPRI specification

- 614.4 Mbps

- 1228.8 Mbps

- 2457.6 Mbps

- 3072 Mbps

- Supports 8b/10b encoding/decoding performed in the PCS/SERDES

- Supports code-violation detection performed in the PCS/SERDES

- Performs CPRI Hyperframe Framing

- Performs interleaving of IQ data, sync, C&M data, and vendor specific information

- Provides an 8-, 16-, or 32-bit parallel interface for IQ data

- Performs subchannel mapping:

- Supports a slow C&M channel based on a serial HDLC interface at standard bit rates (240 Kbps, 480 Kbps,960 Kbps, and 1920 Kbps). The HDLC framer, if needed, must be provided as a separate IP core.

- Supports a fast C&M channel based on a serial Ethernet interface (84.48 Mbps max.) to the user logic, anon-standard rate MII Ethernet interface to a MAC, or a 100 Mbps MII interface to a PHY device. Accepts a user-selected pointer to the CPRI subchannel where the Ethernet link starts. The Ethernet MAC function isprovided as a separate IP core.

Block Diagram

Technical Specifications

Short description

Common Public Radio Interface - IP Core

Vendor

Vendor Name

Related IPs

- Common Public Radio Interface (CPRI) v.4.2 IPC

- Common Public Radio Interface (CPRI) v.5.0 IPC

- Common Public Radio Interface (CPRI) v.6.1 IPC

- Common Public Radio Interface (CPRI) v.7.0 IPC

- Advanced Encryption Standard (AES-128) core with AMBA AHB interface

- Cryptographically Secure Pseudo Random number Generator IP Core