The AXI2APB IP provides chip designers and architects, an efficient way to connect AXI & APB based IPs with reduced latency, power, and area.

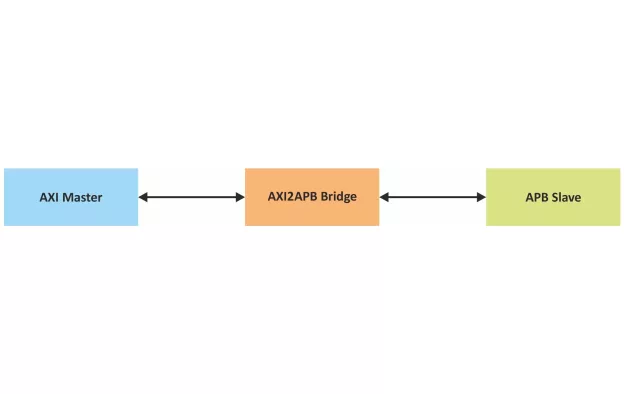

AXI2APB Bridge

Overview

Key Features

- Support AMBA 5/4/3/2 AXI to APB Protocol conversion

- Interversion Transfer conversion like AHB5 to APB4

- Port data width can be different.

- Apart from data width, other protocol supported signals can also have different widths.

- Support all type of transfers

- Early response also possible for write transfer

- Support different phase shifted frequencies for Master and Slave

- Clock enable disable mechanism

- Support logical -physical address conversion

- Both little & high endianness is supported

- Secure Transfer

- Support back to back transfers

Benefits

- Available in native Verilog (RTL)

- Lintin, Synthesis, CDC, RDC are cleaned up.

- Verified with an expert team using comprehensive and Regression Test Suites.

- Consistency of interface, installation, operation, and documentation across all our Ips

- Easy GUI based integration and configuration technique

- 24X5 customer support

- Unique and customizable licensing models

Block Diagram

Deliverables

- Bridge IP

- IP generator & config tool

- Verilog Test Environment with Verilog Testcases

- IP analysis reports

- Linting report

- Synthesis report

- IP-XACT RDL generated address map

- Simulation script

- IP Block Guide

- Quick Start Guide