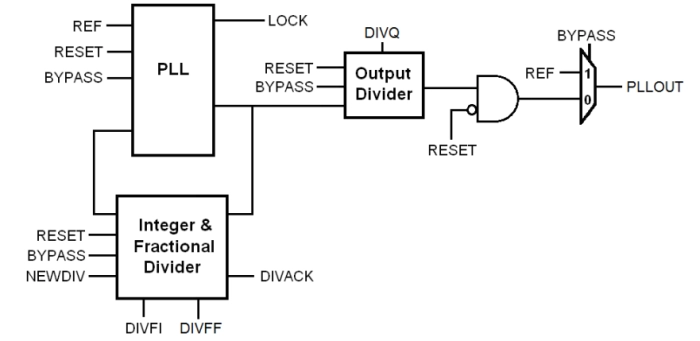

The Fractional-N PLL addresses power sensitive designs required for IOT, mobile and other low power applications needing non-integer clock multiplication, programmable clock synthesis, and clock tracking for fine tuning on-the-fly. The PLLs are designed for digital logic processes and use robust design techniques to work in noisy SoC environments, such as high speed communication to low power consumer to memory interfaces.

The programmable Fractional-N divider allows the PLL to lock to an incoming clock source and produce an output clock with a non-integer multiplication factor. The generated clock can be locked to the input source yet adjusted to a fine-degree of precision, and may be adjusted on-the-fly to maintain a relatively drifting local clock need. The updatable programmable fractional feedback divider is provided for this purpose. “On the fly” capability means the frequency transition and re-obtaining lock process for small frequency adjustment is glitch free and contains limited frequency over/undershoot.

PLL Operational Range Description Symbol Min Typ Max Units Input Frequency FREF 10 60 MHz VCO Frequency FVCO 1200 2400 MHz Output Frequency FOUT 20 1200 MHz Output Duty Cycle tDO 45 55 % Total Area A 0.024 sq. mm Total Power IDD 3.6 mA Operational Voltage (Digital) VDIG 0.99 1.1 1.21 V Operational Voltage (Analog) VANA 2.97 3.3 3.63 V Operational Temperature TOP -40C 25 175 C Table 1: PLL Operational Range AEC-Q100 Ready Grades AEC-Q100 Ready Grade Ambient Temperature Junction Temperature 0 -40°C to +150°C -40°C to +175°C Table 2: AEC-Q100 Ready Grades Supported Metal Stacks Stack Option Stack Name 1 5L1x_1T6x_LB 3 5L1x_2T6x_LB 14 5L1x_2T6x_LB14kA Table 3: Supported Metal Stacks