The ARC-V™ RHX-100 series processors feature a dual-issue, 32-bit superscalar architecture for use in applications where real-time performance is required. The cores offer outstanding performance with a small area footprint and low power consumption.

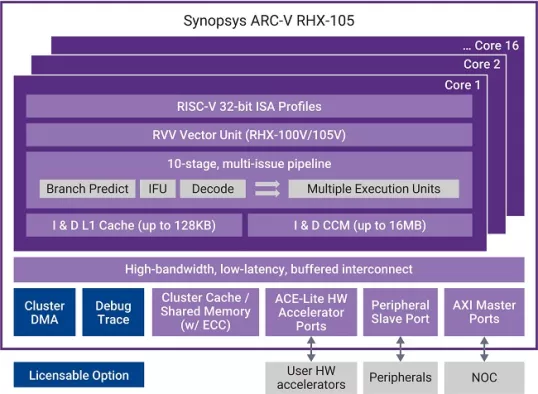

The ARC-V RHX-100 processors are based on the RISC-V instruction set architecture (ISA). The processors feature a 40-bit physical address space and can directly address memories up to 4.5 Petabytes (4.5x1015) in size. For applications requiring higher performance, the multi-core RHX-105 and RHX-105V are available with support for up to 16 CPU cores and up to 16 hardware accelerators in the processor cluster. RISC-V vector extensions (RVV) are available in the RX-100V (single core) and RHX-105V (multi-core) processors.

The ARC-V RHX-100 features level 1 (L1) instruction and data cache and close coupled memory (CCM) and is optimized for use in high-performance real-time embedded applications.