APB UART with optional ISO7816-3

Overview

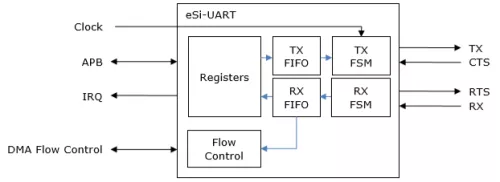

The eSi-UART core can be used to implement asynchronous serial communications. It is ideally suited for implementing RS232 or ISO7816-3 for smartcard based connectivity. The UART is supplied with an AMBA APB slave interface and so can be driven by software or via DMA.

Key Features

- 7 or 8 data bits.

- 1 or 2 stop bits.

- Parity bit (None / Even / Odd / Mark / Space).

- Optional RTS/CTS flow control.

- Programmable bit rate.

- Optional ISO 7816-3 T=0 and T=1 support, with NACK and retry.

- Configurable TX and RX FIFO.

- Programmable receive timeout and transmit guard time.

- AMBA 3 APB slave interface.

- DMA flow-control interface.

Block Diagram

Deliverables

- Verilog RTL

- Testbench

- Simulation and synthesis scripts

- Documentation

- C API

Technical Specifications

Short description

APB UART with optional ISO7816-3

Vendor

Vendor Name

Maturity

Silicon proven in multiple products

Availability

Immediate