Peripheral Component Interconnect (PCI) is a widely accepted bus standard that is used in many applications including telecommunications, embedded systems, high performance peripheral cards, and networking.

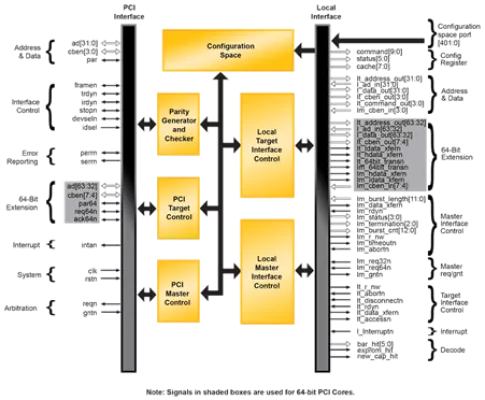

Lattice's PCI IP core provides an ideal solution that meets the needs of today's high performance PCI applications. It is fully compliant with the PCI Local Bus Specification, revision 2.2 for speeds up to 66MHz. The PCI core provides a customizable 32/64-bit master/target or target solution. The core bridges the gap between the PCI interface and a specific design application, providing an integrated PCI solution. The PCI solution allows designers to focus on the application rather than on the PCI specification, resulting in a faster time-to-market.

The Lattice PCI offering is available in a number of configurations covering 32-bit PCI, 64-bit PCI, 32-bit local bus, 64-bit local bus, master/target and target applications. In this document, details of 64-bit operation and master operation only apply when relevant. The appendix to the user's guide shows what cores are available on which devices.

64 Bit PCI Master/Target

Overview

Key Features

- Available as 32/64-Bit PCI Bus and 32/64-Bit Local Bus

- PCI SIG Local Bus Specification, Revision 3.0 Compliant

- 64-Bit Addressing Support (Dual Address Cycle)

- Capabilities List Pointer Support

- Parity Error Detection

- Up to Six Base Address Registers (BARs)

- Fast Back-to-Back Transaction Support

- Supports Zero Wait State Transactions

- Special Cycle Transaction Support

- Customizable Configuration Space

- Up to 66MHz PCI

- Fully Synchronous Design

Block Diagram

Technical Specifications

Short description

64 Bit PCI Master/Target

Vendor

Vendor Name