32-bit PCI Bus Target

Key Features

- Fully supports PCI specification 2.1 and 2.2 protocol.

- Designed for ASIC and PLD implementations.

- Fully static design with edge triggered flip-flops.

- Efficient back-end interface for different types of user devices.

- Supports compact PCI, Cardbus, Mini-PCI and Power Management.

- Supports zero wait state data burst transfer to maximize memory bandwidth.

- Zero wait state and user inserted wait state burst data transfer.

- Dual write buffer supports write data posting.

- User controlled burst and non-burst data transfer.

- Multiple address mapping to memory and IO address spaces.

- Automatic handling of configuration register read/write access.

- Supports back-end initiated target retry, disconnect and abort.

- Supports delayed data transaction initiated by user logic.

- Parity generation and parity error detection.

- Includes all PCI specific configuration registers.

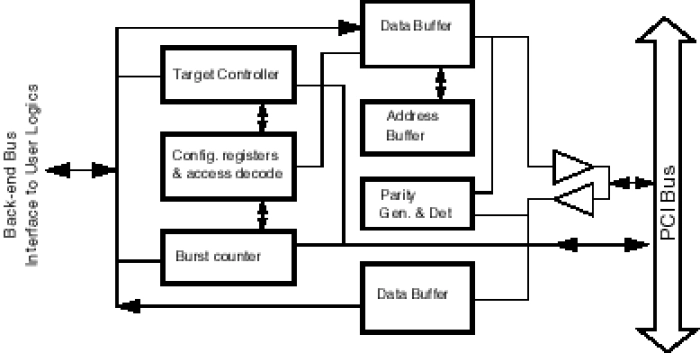

Block Diagram

Technical Specifications

Short description

32-bit PCI Bus Target

Vendor

Vendor Name

Availability

Now