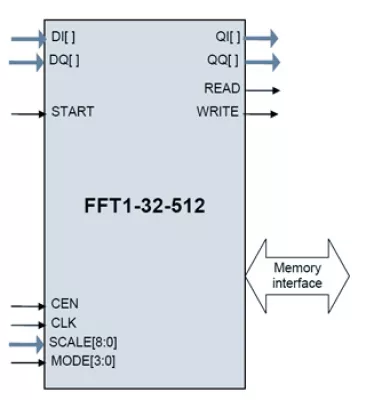

32-512 Point Streaming FFT

Overview

The FFT1-32-512/4 core implements 32, 64, 128, 256, and 512 point FFT and IFFT in hardware that runs at the clock frequency four times higher than the input sampling frequency.

Key Features

- Supports 32/64/128/256/512-point complex FFT and IFFT and can switch dynamically

- Inputs and outputs data in the natural order

- Throughput of 1 sample (In-phase I + quadrature Q) per 4 clocks; no-gap processing of the input data

- Parameterized bit width.

- Test bench and bit-accurate model

- Available in ASIC and FPGA technologies

- Minimal gate count implementation

- Programmable inter-stage scaling register

Block Diagram

Applications

- Communication System

- Signal Analysis

Deliverables

- Synthesizable Verilog RTL source code

- Bit-accurate software model

- Simulation scripts

- Self-checking environment

- Test-bench

- Test-vectors

- Expected Results

- User Manual

Technical Specifications

Availability

Now