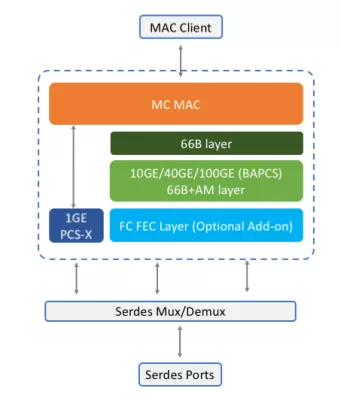

The 1G-100G Multi-channel Multi-rate Ethernet/FiberChannel/FlexO Core (OmegaCORE100G_ZX) core from Alphawave is a multi-rate Ethernet aggregator that supports tributaries at 1GE, 10GE, 25GE, 40GE, 50GE, 100GE in combinations up to 100G for OmegaCORE100G_ZX.

This core implements multi-rate Ethernet PCS and MAC. This versatile device allows users to add or drop sub-channels (for example 10GE) or merge channels (for example 4x25G = 100GE). These dynamic changes do not affect traffic on existing channels.

The north-bound interface from the multi-channel MAC provides a configurable system interface. The Multi-channel MAC manages the mapping between individual MACs and the assigned I/O or I/O group.

The southbound interface is mapped (at the PMA layer) to the on-chip SERDES. The core is responsible for channel alignment and FEC (where applicable).

1G-100G Ethernet/FiberChannel/FlexO Core

Overview

Key Features

- Support any ethernet combinations (table 1) to maximum data-rate of the device

- Fully compatible with IEEE802.3 2015 and IEEE 802.3 Standards

- Optional add-on of ultra Low latency and area efficient FEC Core supports FC FEC RS (2112, 20280)

- Support HiGig, HiGig+ and HiGig-lite

- Optional Add-on with 66B ports to support FC800, FC1200 and FC1600 and their FC2 Monitoring

- Support 1588v2 time stamps and full error handling

- Support 802.1Qbb priority flow control (PFC)

- 100G/50G/40G/25G/10G BASE-R PCS Core Features

- PCS TX Core

- X58 Scrambling (optional bypass)

- 64B/66B encoding of incoming MII signal (for 10GE+)

- Idle block removal (to reduce overhead for AM insertion)

- 8B10B encoding (for 1GE)

- Alignment Marker (AM) insertion. Unique marker portion of AM for each lane is software configurable.

- Test pattern generation (scrambled idles)

- Clause 45 MDIO register set

- Error detection and interrupt reporting

- Optional add-on FC FEC encoder

- PCS RX Core

- 64B/66B decoding to MII signal (for 10GE+)

- 8B10B decoding and sync (for 1GE)

- X58 De-scrambling (optional bypass)

- Alignment marker removal (where applicable)

- Unique marker portion of AM for each lane is software configurable (where applicable)

- Test pattern monitoring

- Clause 45 MDIO register set

- Error detection and interrupt reporting

- Loopback from TX MII to RX MII

- Performance Monitoring and Statistics

- Dynamic skew measurement for each lane

- PCS Status – link up/down

- High bit error rate (hi-BER)

- BER counter

- Test pattern error counter

- Multi-lane AM status (locked and aligned/not locked and aligned)

- Optional Add-on

- FEC Corrected code word count (with FEC enabled)

- FEC corrected 1s and 0s

- FEC Uncorrected code word count (with FEC enabled)

- FEC symbol error counter (with FEC enabled)

- 100G/50G/40G/25G/10G MAC Core Features (per channel)

- TX FCS insertion

- TX MAC control frame generation

- Unicast/Multicast PAUSE frame generation by MAC client or by software

- Software configurable PAUSE quanta

- TX Performance Monitoring and Statistics (counters are 36-bit to accommodate 1-second of statistic counts)

- Byte count

- Frame count

- PAUSE frame count

- Multicast frame count

- Unicast frame count

- Undersize frame count

- Oversize frame count

- Frame count statistic for the following sized frames:

- 64

- 65-127

- 128-255

- 256-511

- 512-1023

- 1024-1518

- 1519-1522

- 1523-1548

- 1549-2047

- 2048-4095

- 4096-8191

- 8192-9215

- RX FCS check and removal

- RX PAUSE frame processing and handling

- RX Performance Monitoring and Statistics (counters are 36-bit to accommodate 1-second of statistic counts)

- Bad FCS

- Bad Preamble

- Byte count

- Frame count

- PAUSE frame count

- Multicast frame count

- Unicast frame count

- Bad FCS frame count

- Bad frame count

- Bad aligned frame count

- Undersize frame count

- Oversize frame count

- Frame count statistic for the following sized frames:

- 64 byte

- 65-127

- 128-255

- 256-511

- 512-1023

- 1024-1518

- 1519-1522

- 1523-1548

- 1549-2047

- 2048-4095

- 4096-8191

- 8192-9215

- Additional Add-on features

- HiGig, HiGig+ and HiGig-lite

- FC1200 to FC1600 FC2 Monitoring

- 1588v2 time stamping

- 802.1Qbb Priority Flow Control (PFC) up to 8 priorities

Benefits

- Combines Ethernet streams at a variety of rates to a single multi-channel interface at the MAC

- The Epak100_ZX allows access connections supporting 1GE, 10GE, 25GE, 40GE, 50GE and 100GE in any combination on any port or groups of ports to a maximum total bandwidth of 100Gbps

- Dynamically change rate on any port without affecting existing traffic

- Off-the-shelf, proven technology implementation in ASIC SOC

- Tested and interoperability-proven against Spirent and Viavi test equipment

Block Diagram