DVB IP Core

Welcome to the ultimate DVB IP Core IP hub! Explore our vast directory of DVB IP Core IP

All offers in

DVB IP Core

Filter

Compare

79

DVB IP Core

from 20 vendors

(1

-

10)

-

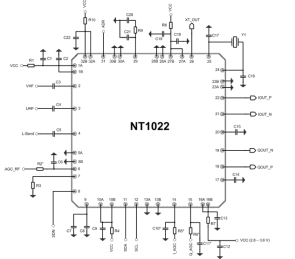

VHF/ UHF/L (DVB-H, DMB and ISDB-T) RF Front-end

- TSMC BiCMOS SiGe 180 nm technology

- Direct conversion receiver

- A few number of external components

- 0.18 um SiGe BiCMOS technology

-

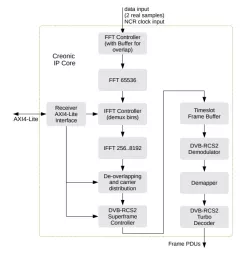

DVB-RCS2 Multi-Carrier Receiver

- Compliant with ETSI EN 301 545-2 (DVB-RCS2)

- Support for Linear Modulation Bursts of Table A-1

- Optional support for Spread-spectrum Linear Modulation Burst waveforms of Table A-2

- Support for BPSK, QPSK, 8-PSK, 16-QAM

-

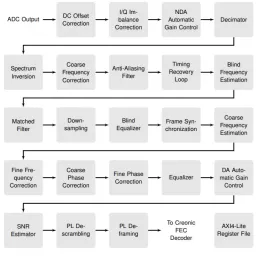

DVB-S2X Demodulator

- Compliant with DVB-S2 and DVB-S2X

- Supports ACM, CCM, and VCM modes

- Support for short and long blocks (16,200 bits and 64,800 bits)

- Support for QPSK to 256-APSK

-

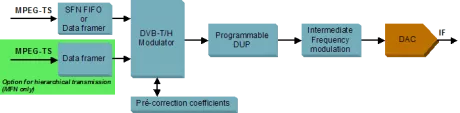

DVB-T/H Modulator

- ETSI, DVB-T/H (EN 300 744 V1.5.1) Compliant baseband transmitter for Digital Terrestrial Television

- · The MVD modulator cores can be delivered with an Intermediate Frequency output or a RF output when using Analog Devices or Maxim RF DACs (see separate datasheet, available on request)

- · Drop-in module for Xilinx Spartan-6, Virtex-6, Artix-7, Kintex-7, Virtex-7, Zynq FPGAs

- · Single clock (up to 140 MHz+ for Spartan-3/6™, 180 MHz+ for Virtex-5/6™)

-

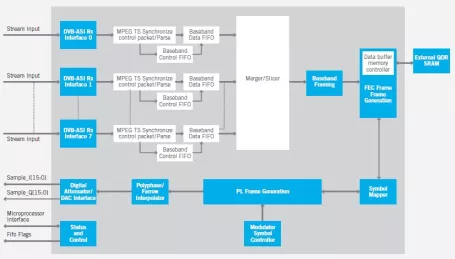

Multistream DVB-S2 Modulator

- Aggregation of up to 8 input streams

- Complete user control to choose any number of streams

- Each stream independently configurable

- DVB-S2 CCM and VCM operations

-

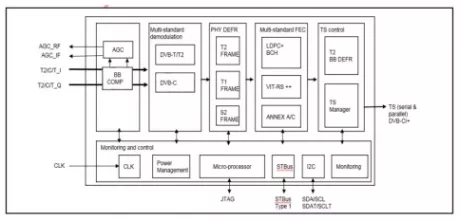

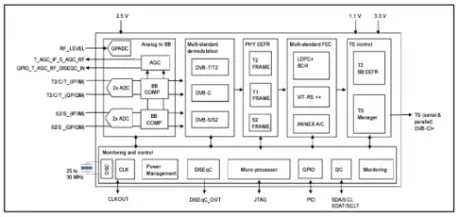

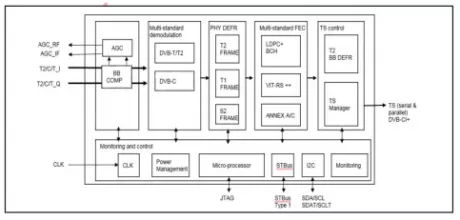

DVB-S2/S/T2/T/C Combo Demodulator IP (Silicon Proven)

- Combines a configurable DVB-T2/T/C/S/S2 demodulator.

- AGC derived from IF

- Low-power process, design and architecture

- Includes full suite of low-level drivers and application software, detailed user manuals and reference design schematics

-

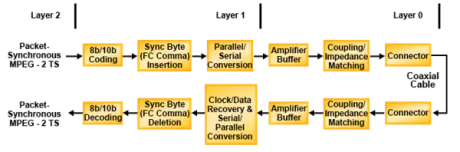

Digital Video Broadcasting - (DVB-ASI) IP Core

- Configurable Tx FIFO supporting independent Layer 2 transmit clock

- Configurable Rx FIFO supporting independent Layer 2 receive clock

- Automatic start of packet comma insertion in the transmit side

- Rate-matching comma insertion in the transmit side

-

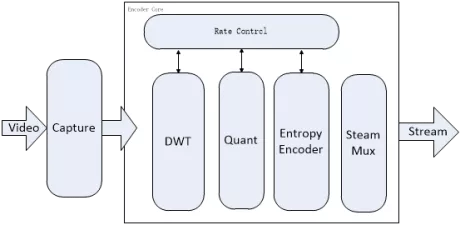

ISO/IEC 21122-1 JPEG-XS Standard Codec

- Support YUV444/ YUV422 input format

- Support color depth: 8bit / 10bit(optional) /12 bit(optional).

- Multi-Channel (optional)

- Visual Lossless compression

-

DVB-C Demodulator IP (Silicon Proven)

- QAM and FEC solution

- ITU-T J.83 Annexes A/B/C, DVB-C specification (ETSI 300 429)

- Nordig Unified v2.4 and SARFT compliant

- Up to 7.2 Ms/s symbol rate

-

DVB-T2/T Demodulator and Decoder IP (Silicon Proven)

- DVB-T2 with T2-base profile of ETSI EN- 302755 v1.3.1,DTG7 v3 and Nordig Unified v2.4 compliant, 1.7-5-6-7 and 8 MHz normal and extended BW signals supported, GS streams, FEF and MISO supported

- DVB-T demodulator: Compliant with ETSI EN-300744 v1.5.1, DTG7 v3 and Nordig Unified v2.4 compliant, 6-7 and 8 MHz BW supported

- DVB-T/T2 compatible with zero-high- and legacy-IF tuners (CAN or silicon)

- Embedded microcontroller (DVB-T2 task sequencing by firmware and monitoring)