TSMC N3E IP

Filter

Compare

76

IP

from

3

vendors

(1

-

10)

-

TSMC N3E 3.3V GPIO

- Synopsys’ General-Purpose I/O (GPIO) Library IP provides designers with the input/output operation, functionality, and reliability required for their SoCs targeting mobile, automotive, and high-performance computing (HPC) applications

- The IP is silicon-proven and available in several foundries and process technologies from 3nm to 22nm

- Synopsys GPIO library is designed to support multiple voltages; it offers a complete set of support cells (supply, corner spacers, diode breakers, terminators) required to create complete I/O pad rings for system-on-chips (SoCs)

- The library is compatible with flip-chip packaging

-

TSMC N3E 1.2V GPIO

- Synopsys’ General-Purpose I/O (GPIO) Library IP provides designers with the input/output operation, functionality, and reliability required for their SoCs targeting mobile, automotive, and high-performance computing (HPC) applications

- The IP is silicon-proven and available in several foundries and process technologies from 3nm to 22nm

- Synopsys GPIO library is designed to support multiple voltages; it offers a complete set of support cells (supply, corner spacers, diode breakers, terminators) required to create complete I/O pad rings for system-on-chips (SoCs)

- The library is compatible with flip-chip packaging

-

TSMC N3E SD/eMMC PHY North/South Poly Orientation

- Synopsys SD/eMMC PHY provides an optimal balance for cost and performance for storage solutions

- Synopsys SD/eMMC PHY is a hard IP that can be used to implement a single interface that can accomplish 4-bit, 8-bit eMMC & 4-bit SD operations

- It includes an optional digi logic circuitry which is required for high-speed operations

- It complies with eMMC 5.1 (JESD84-B51A) and SDIO 6.0 JEDEC standards

-

TSMC N3E 1.5V LVDS MS Add-on

- Synopsys Low Voltage Differential Signaling (LVDS) IO library is a high-frequency interface that uses differential signals for data transmission

- A few typical LVDS IO applications are in display monitors, printers, high-speed clock transfers, and high-speed SERDES

- Synopsys LVDS IO library is used to build an LVDS-based interface for high-speed interconnect applications

- This library is designed to optimize IO performance with a core voltage of 0.75 V and supports an IO supply voltage of 1.2V/1.5 V

-

TSMC N3E 1.2V LVDS MS Add-on

- Synopsys Low Voltage Differential Signaling (LVDS) IO library is a high-frequency interface that uses differential signals for data transmission

- A few typical LVDS IO applications are in display monitors, printers, high-speed clock transfers, and high-speed SERDES

- Synopsys LVDS IO library is used to build an LVDS-based interface for high-speed interconnect applications

- This library is designed to optimize IO performance with a core voltage of 0.75 V and supports an IO supply voltage of 1.2V/1.5 V

-

TSMC N3E 1.2V/1.8V OSC METAL STACK ADD ON

- Synopsys offers low jitter Programmable Crystal Oscillator that supports 5 MHz to 50 MHz, with optimized design to reduce jitter and to support wide operation

- In addition, the bypass mode is supported with a maximum frequency of 50 MHz

-

TSMC N3E 1.2V/1.8V OSC

- Synopsys offers low jitter Programmable Crystal Oscillator that supports 5 MHz to 50 MHz, with optimized design to reduce jitter and to support wide operation

- In addition, the bypass mode is supported with a maximum frequency of 50 MHz

-

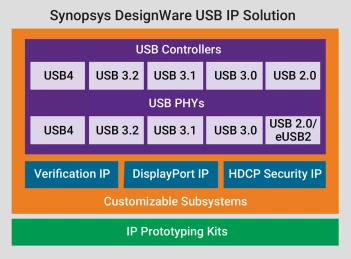

USB4 PHY - TSMC N3E 1.2V, North/South Poly Orientation

- Supports 40 Gbps, 20 Gbps, 10 Gbps, and 5 Gbps data rates

- Supports 480 Mbps, 12 Mbps, and 1.5 Mbps data rates

- x1 and x2 configurations (USB 3.2 and USB 3.1 PHY only)

- Low active and standby power

- Small area for low silicon cost