TSMC 3nm IP

Filter

Compare

105

IP

from

7

vendors

(1

-

10)

-

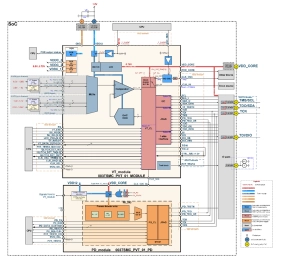

Process/Voltage/Temperature Sensor with Self-calibration (Supply voltage 1.2V) - TSMC 3nm N3P

- 003TSMC_PVT_01 IP library is a unique solution intended to continuously monitor IC status at several on-die locations.

- It is able to detect manufacturing process deviation, perform voltage, current and die temperature measurement.

-

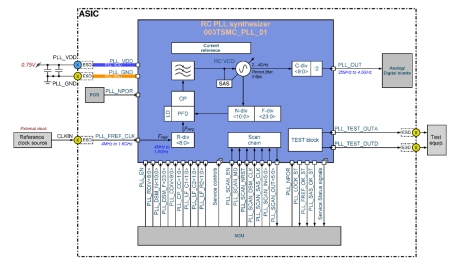

25MHz to 4.0GHz Fractional-N RC PLL Synthesizer on TSMC 3nm N3P

- Fractional-N Phase locked loop frequency synthesizer is intended for ASIC clock generation.

- The Fractional-N PLL loop with 2GHz-4GHz VCO has high phase noise performance and ultra-fine frequency tuning step.

- VCO Sub-band auto select (SAS) system allows to find automatically appropriate sub-band for VCO on locked PLL.

-

224G Ethernet PHY for TSMC 3nm

- Supports full-duplex 1.25 to 224Gbps data rates

- Enables 200G, 400G, 800G, and 1.6T Ethernet

- Ethernet interconnects for wired network infrastructure

-

TSMC 3nm (N3E) 1.8V SD/eMMC PHY, multiple metalstacks

- Completely hardened PHY solution along with programmable delay chains & I/Os

- Fully selectable output impedance

- Compliant with eMMC 5.1 (JESD84-B51A) and SDIO 3.0 JEDEC Standard

- Automotive G1/G2 supported, ASIL-B certified

-

TSMC 3nm (N3E) 1.8V SD/eMMC IO

- Completely hardened PHY solution along with programmable delay chains & I/Os

- Fully selectable output impedance

- Compliant with eMMC 5.1 (JESD84-B51A) and SDIO 3.0 JEDEC Standard

- Automotive G1/G2 supported, ASIL-B certified

-

TSMC CLN3PLVT 3nm Ultra PLL - 15MHz-3000MHz

- New state-of-the-art architecture using high-speed digital and analog circuits that offers unprecedented operating ranges and extremely high performance.

- Ultra low jitter performance for the most demanding SerDes and ADC reference clocks.

- Ultra wide frequency range with multiplication factors over 250,000 to support 32KHz to 1GHz references.

- Precise frequency control with a least 26 fractional bits (at least 10 precise) for extremely high fractional-N resolution.

-

TSMC CLN3PLVT 3nm Spread Spectrum PLL - 262MHz-1310MHz

- Designed for PC, networking, and consumer-electronics applications where spread-spectrum clock sources are required to satisfy FCC requirements for peak RF spectral emissions.

- Spreading rate and spreading depth are precisely adjustable to allow the designer to dial-in the desired characteristics.

- 15-bit fractional-N feedback divider with 4 bits of precise control.

- Available with multi-phase outputs.

-

TSMC CLN3PLVT 3nm Spread Spectrum PLL - 524MHz-2620MHz

- Designed for PC, networking, and consumer-electronics applications where spread-spectrum clock sources are required to satisfy FCC requirements for peak RF spectral emissions.

- Spreading rate and spreading depth are precisely adjustable to allow the designer to dial-in the desired characteristics.

- 15-bit fractional-N feedback divider with 4 bits of precise control.

- Available with multi-phase outputs.