SPI 5 IP

Filter

Compare

138

IP

from

46

vendors

(1

-

10)

-

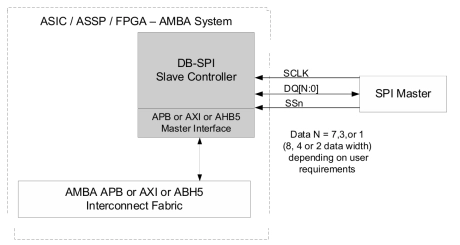

SPI Slave IP transfers to/from a AMBA APB, AXI, or AHB Interconnect

- The DB-SPI-S-AMBA-BRIDGE is a Serial Peripheral Interface (SPI) Controller Verilog IP Core supporting only Slave SPI Bus transfers (both Full Duplex and Half Duplex) to/from a AMBA APB, AXI, or AHB Interconnect.

- The DB-SPI-S-AMBA-BRIDGE contains dual clock Transmit/Receive FIFOs and Finite State Machine control to process incoming SPI transmit/receive transactions, and a AMBA Master Interface (i.e. APB, AXI, AHB5) to read or write the SPI payload data with respect to the AMBA Interconnect. No processor is required for configuration or control; the DB-SPI-S-AMBA-BRIDGE operates autonomously from reset.

-

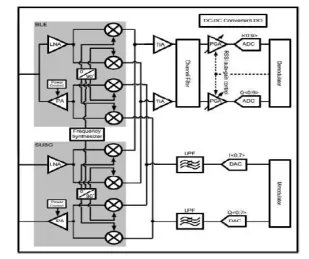

BLE 5 / Sub-1GHz / 15.4/ SoC Companion Chip

- RF Front end SoC with integrated modem:

- 2.4GHz - Bluetooth Low Energy v5.x with Link Layer Integrated

- 15.4 / ZigBee & 15.4G

- 150-960MHz - Sub-1GHz ISM

-

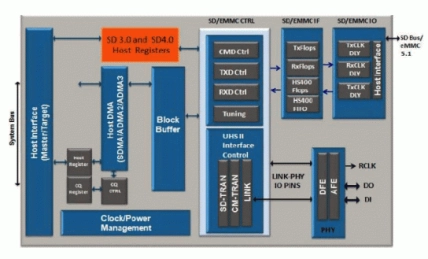

SD 4.1 eMMC 5.1 Dual Host Controller IP

- The SD 4.1/SDIO 4.0/eMMC 5.0 Host IP from Arasan Chip Systems is a highly integrated host controller IP solution that supports three key memory card I/O technologies:

- The SD 4.1 / eMMC 5.1 Host IP handles all of the timing and interface protocol requirements to access these media as well as processing the commands in hardware thereby scaling in both performance and access speeds. The IP supports connection to a single slot and performs multi-block writes and erases that lower access overhead. In addition, a host can utilize this IP to boot directly from an attached eMMC memory, thereby simplifying system initialization during power up. The host interface is based on a standard 32-bit AHB bus which is used to transfer data and configure the SD 4.1 / eMMC5.1 Host IP.

- eMMC 5.1 is backward compatible to the previous versions.

-

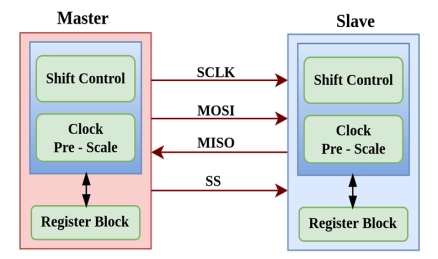

SPI - Function Controller

- The SPI protocol specification supports high speed data transfer as per the peripheral specification, making it ideal for high - performance applications that require fast data transfer rates.

-

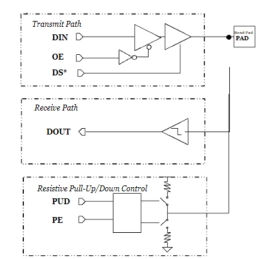

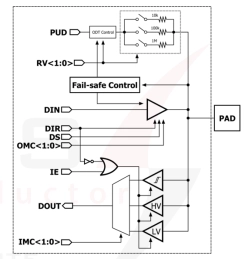

1.8V/3.3V I/O library with ODIO and 5V HPD in TSMC 16nm

- A 1.8V/3.3V flip-chip I/O library with 4kV HBM ESD protection, I2C compliant ODIO and Hot-Plug Detect.

- This library is a production-quality, silicon-proven I/O library in TSMC 16nm technology.

- Supports multi-voltage GPIOs, capable of operating at 1.8V or 3.3V, dynamically selectable at the system level.

-

-

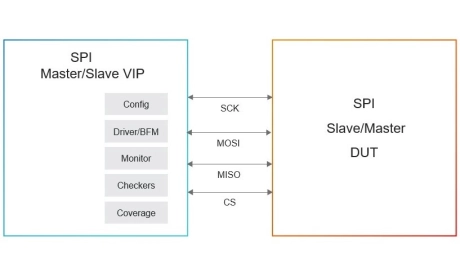

Simulation VIP for SPI

- Full Duplex

- Simultaneous transfer from Manager and Subordinate

- Variable Size Shift Registers

- 8, 16, and 32-bit shift register for Tx and Rx

-

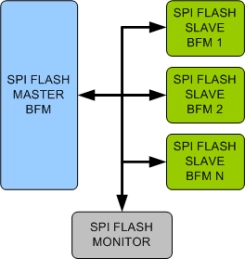

SPI (Serial Peripheral Interface) Flash Verification IP

- Fully compatible with SPI Flash standards.

- Supports SQI interface specification and common flash device models.

- Follows Serial Flash specification as defined in WINBOND, MICRONIC, MACRONIX, MICRON, SPANSION, Silicon Storage technology (SST) and many more.

- Supports single, dual and quad mode bus width operation.

-

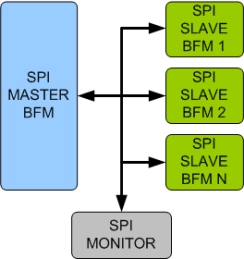

SPI (Serial Peripheral Interface) Verification IP

- Follows SPI basic specification as defined in SPI Block Guide V04.01

- Supports SQI interface specification and common flash device models

- Supports data width from 4 bits to 64 bits.

- Supports Master and Slave Mode

-

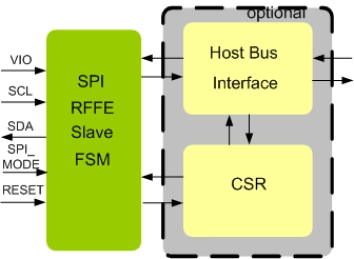

MIPI RFFE SPI Slave IIP

- Compliant with 3.0 MIPI RFFE Specification and SPI Block Guide V04.01 Specification

- Full MIPI RFFE Slave functionality.

- Supports following frames

- Command Frame