RISC-V processor trace IP

Filter

Compare

44

IP

from

10

vendors

(1

-

10)

-

Vector-Capable Embedded RISC-V Processor

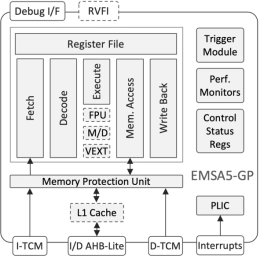

- The EMSA5-GP is a highly-featured 32-bit RISC-V embedded processor IP core optimized for processing-demanding applications.

- It is equipped with floating-point and vector-processing units, cache memories, and is suitable for concurrent execution in a multi-processor environment.

-

-

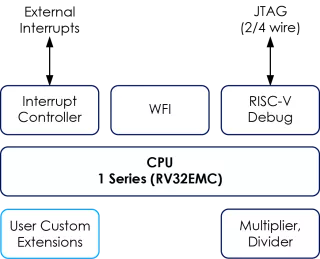

32 bit - Compact RISC-V Processor Core

- 32-bit RISC-V core

- RV32EMC instruction set

- 16 general purpose registers

-

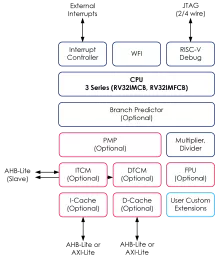

Compact RISC-V Processor - 32 bit, 3-stage pipeline, 32 registers

- 32-bit RISC-V core

- Available in two versions:

- 32 general purpose registers

- Either parallel multiplier

-

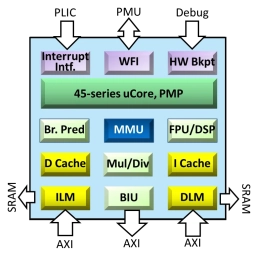

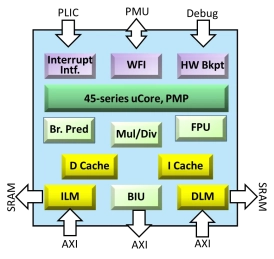

8-stage superscalar RISC-V processor

- The 64-bit AX45 is an 8-stage superscalar processor that supports RISC-V specification, including “G” (“IMAFD”) standard instructions, “C” 16-bit compression instructions, “P” Packed-SIMD/DSP instructions, “B” bit manipulation, and Andes performance enhancements, plus Andes Custom Extension™ (ACE) for user-defined instructions.

-

64-Bit 8-stage superscalar RISC-V processor

- 64-bit in-order dual-issue 8-stage pipeline CPU architecture

- AndeStar™ V5 Instruction Set Architecture (ISA)

- 16/32-bit mixable instruction format for compacting code density

- Advanced low power branch predication to speed up control code

- Return Address Stack (RAS) to accelerate procedure returns

-

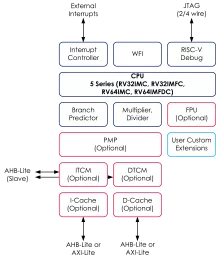

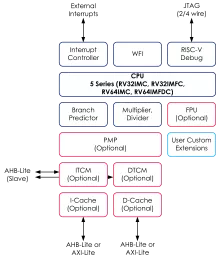

Compact, efficient 64-bit RISC-V processor with 5-stage pipeline

- Support for RV32IM

- 5-stage pipeline

- Thirty-two 64-bit general purpose registers

-

RISC-V processor - 32 bit, 5-stage pipeline

- Support for RV32IM/RV64IM

- 5-stage pipeline

- 32 or 64bit general purpose registers

-

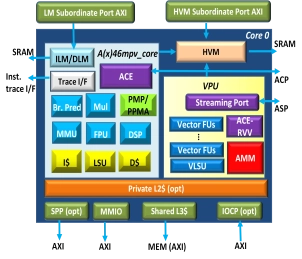

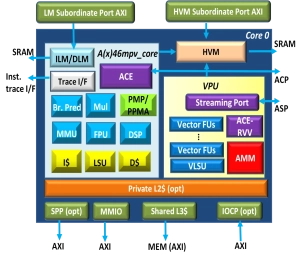

64 bit RISC-V Multicore Processor with 2048-bit VLEN and AMM

- 2 different packages with or without vector: AX46MPV, AX46MP

- in-order dual-issue 8-stage CPU core with up to 2048-bit VLEN

- Symmetric multiprocessing up to 16 cores

- Private Level-2 cache

- Shared L3 cache and coherence support

-

32 bit RISC-V Multicore Processor with 256-bit VLEN and AMM

- AndesCore™ A46MP(V) 32-bit multicore CPU IP is an 8-stage superscalar processor with Vector Processing Unit (VPU) based on AndeStar™ V5 architecture and Andes Matrix Multiply (AMM) extension.

- It supports RISC-V standard “G (IMA-FD)”, “ZC” compression, “B” bit manipulation, DSP/SIMD ‘P’ (draft), “V” (vector), CMO (cache management) extensions, Andes performance enhancements, plus Andes Custom Extension™ (ACE) for user-defined instructions.