32-bit Ultra Low Power FFT IP

Filter

Compare

1

IP

from

1

vendors

(1

-

1)

-

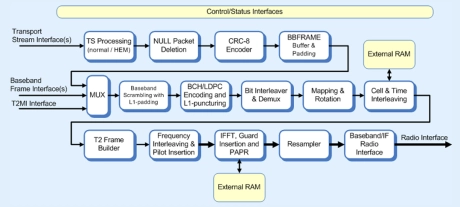

DVB-T2 modulator

- 1k, 2k, 4k, 8k, 16k and 32k OFDM.

- BPSK, QPSK, QAM-16, QAM-64 and QAM-256 support.

- Variable 1·7-10MHz bandwidth interpolation.

- Automatic L1 field padding and puncturing.