1.6T Ethernet IP

Filter

Compare

16

IP

from

6

vendors

(1

-

10)

-

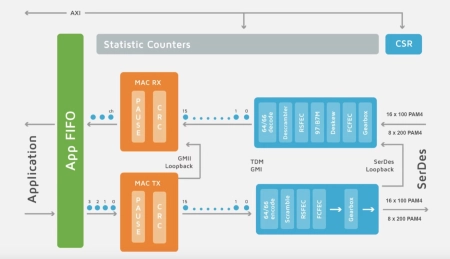

1.6T Ethernet UMAC

- Simple programming and bringing up sequence matching previous UMAC generations

- Support for arbitrary mixed modes across channels and dynamic mode switching

- Support for 224G SerDes

- Standard and priority pause generation, termination, and pass-through

- Support for jumbo frames up to 16K bytes

- TX runt frame padding and RX runt frame stripping

- Counters and interrupts for MIBs and various MAC and PCS/FEC events

-

1.6T Ethernet PCS IP

- Supports all required features of the IEEE 802.3 specification and draft specifications

- IP available in single 1.6T mode and quad channel mode supporting 4 x 400G, 2 x 800G and 1.6T

- Designed to be used with Synopsys 1.6T MAC IP for 1.6T Ethernet Systems

- Includes RS-FEC functions

-

1.6T Ethernet MAC IP

- Supports all required features of the IEEE 802.3 specification

- Supports IEEE-managed objects, IETF MIB-II and RMON for management applications

- Application interface includes the Synopsys native interface 512-bit or 1024bit FIFO for more than 200G operation

- Integration tested with Synopsys 1.6T Ethernet PCS IP and 224G Ethernet PHY IP

-

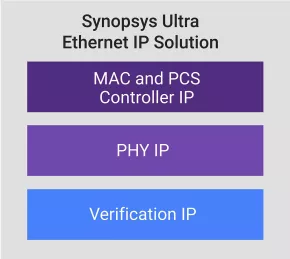

Complete 1.6T Ultra Ethernet IP Solution

- Ethernet MAC, PCS and PHY to complete a full Ultra Ethernet interface stack

- Supports evolving IEEE 802.3 and OIF-224G electrical standards

- Provides support for 4 x 400G, 2 x 800G, and 1.6T Ethernet rates using 112Gbps and 224Gbps SerDes

- Meets performance criteria for chip-to-chip, chip-to-module, and long reach copper/backplane interconnects

-

HPC MACsec Security Modules for Ethernet

- IEEE 802.1ae, IEEE 802.1br Support

- 100 Gbps—1.6 Tbps

- Can reach higher throughputs scalable to 3.2 Tbps

- Supports also lower performance modes down to 10 Gbps

-

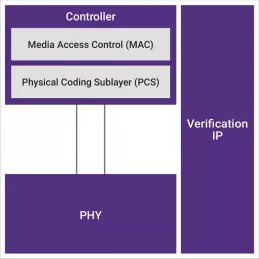

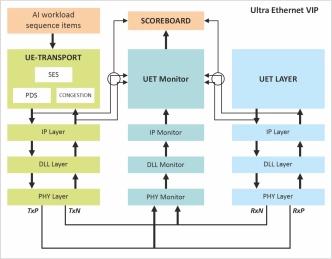

Ultra Ethernet Verification IP

- The Ultra Ethernet (UE) Verification IP provides an effective & efficient way to verify the components interfacing with Ethernet interface of an IP or SoC.

- The UE VIP is compliant with IEEE standard 802.3-2018 & UE Specifications V1.0.

- This VIP is light weight with easy plug-and-play interface so that there is no hit on the design cycle time.

-

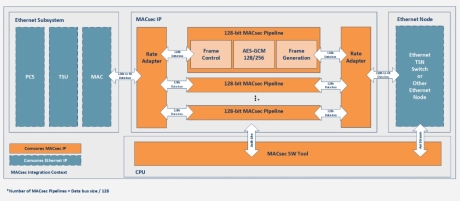

100G / 200G / 400G / 800G / 1.6T MACsec

- The MACsec IP provides Ethernet Layer 2 Security for port authentication, data confidentiality and data integrity as standardized in IEEE 802.1AE.

- It protects components in Ethernet networks especially very high-speed Ethernet used in cloud, data center, and backhaul networks.

- The MACsec IP is a fully compliant solution that provides line-rate encryption and supports VLAN-in-Clear.

-

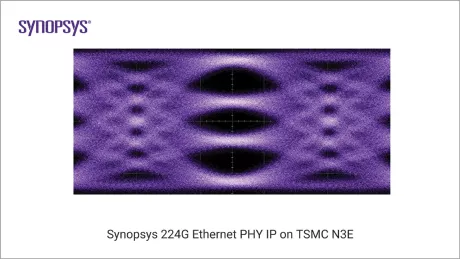

224G Ethernet PHY, TSMC N3P x1, North/South (vertical) poly orientation

- Supports full-duplex 1.25 to 224Gbps data rates

- Enables 200G, 400G, 800G, and 1.6T Ethernet

- Ethernet interconnects for wired network infrastructure

- Supports IEEE 802.3 and OIF-224G standards electrical specifications

-

224G Ethernet PHY, TSMC N2P x4, North/South (vertical) poly orientation

- Supports full-duplex 1.25 to 224Gbps data rates

- Enables 200G, 400G, 800G, and 1.6T Ethernet

- Ethernet interconnects for wired network infrastructure

- Supports IEEE 802.3 and OIF-224G standards electrical specifications

-

224G Ethernet PHY, Intel 18A x4, North/South (vertical) poly orientation

- Supports full-duplex 1.25 to 224Gbps data rates

- Enables 200G, 400G, 800G, and 1.6T Ethernet

- Ethernet interconnects for wired network infrastructure

- Supports IEEE 802.3 and OIF-224G standards electrical specifications