Corigine provides USB 2.0, USB 3.0, USB 3.1 Gen 1, and USB 3.1 Gen 2 controllers that are USB-IF certified, which few suppliers can claim. Corigine's SuperSpeed and Superspeed+ 3.1 USB IP is based on the USB 3.1 specification from the USB Implementers Forum (USB-IF). USB-IF certification reduces the risk of IP design errors due to specification interpretations. Corigine USB controllers are based on a next generation architecture which can fully take advantage of the latest USB features, while maintaining the smallest size, lowest power, and maximum configurability.

Corigine's USB controllers comes with their own UVM-based test suites and are rigorously tested with third-party verification IP (VIP). Utilizing third-party VIP in the verification environment ensures independence from design and verification which is critical for robustness. For system integration and rapid software development, Corigine offers an FPGA development board with industry standard PHYs allowing the connection to real world devices and hosts.

The Corigine USB designer team have been developing USB controllers for many years. The team has leveraged their expertise to develop the next generation USB controllers delivering the most cost-effective, fully compliant SuperSpeed USB IP solution.

USB 3.1 SuperSpeed+ (Gen2) Device Controller (USB-IF Certified)

Overview

Key Features

- USB-IF Certified full-feature Device Controller solution.

- Next generation USB controller architecture producing the smallest size, lowest power, and maximum configurability

- Compliant with USB 3.1 specification revision 1.0 with latest ECNs

- Compliant with xHCI specification revision 1.1

- Supports SuperSpeed+ USB 3.1 at 10 Gbps, SuperSpeed USB 3.0 at 5 Gbps , High-Speed and Full-Speed USB (USB 2.0)

- Optional Multi-Port configurations for both USB2 and USB3.x ports

- Industry standard AMBA interfaces, can be easily integrated into SoC

- AMBA AXI3/AXI4 as DMA Master Interface

- AMBA AXI3/AXI4/AHB/APB as DMA Slave Interface

- Support 16/32/64-bit PIPE Interface, 8/16-bit UTMI+ Interface and 8-bit ULPI Interface, to guarantee compatibility with all USB 2.0 & USB 3.x PHYs

- Highly configurable architecture to achieve the most optimized size and power for target applications

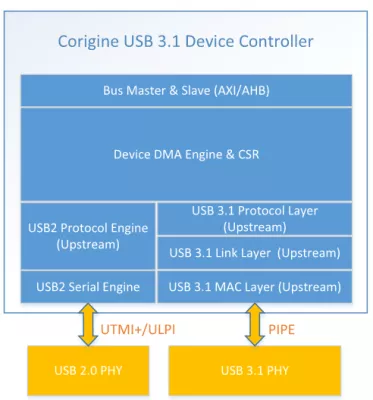

Block Diagram

Deliverables

- Fully Synthesizable RTL

- Synthesis constraints and scripts

- UVM-based verification environment with test cases for SoC integration

- Bare-metal Test Code in C-language, for SoC-level simulation with CPU and chip bring-up after tape-out

- FPGA Platform & Third-Party PHYs cards for evaluation

- User Manual and Integration Guide

- Linux Driver

Technical Specifications

Short description

USB 3.1 SuperSpeed+ (Gen2) Device Controller (USB-IF Certified)

Vendor

Vendor Name

Maturity

Available on request

Availability

May 2017

Related IPs

- USB 3.1 SuperSpeed+ (Gen2) PC Host Controller (USB-IF Certified)

- USB 3.1 SuperSpeed+ (Gen2) Dual-Role Device Controller (USB-IF Certified)

- USB 3.1 SuperSpeed PC Host Controller (USB-IF Certified)

- USB 3.1 SuperSpeed Device Controller (USB-IF Certified)

- USB 3.1 SuperSpeed Dual-Role Device Controller (USB-IF Certified)

- USB 3.1 SuperSpeed Embedded Host Controller (USB-IF Certified)