Vendor:

Atria Logic, Inc.

Category:

USB

USB 2.0 CONTROLLER IP CORE

The AL-USB2D-CTRL fully synthesizable core implements a high/full-speed (480Mbps/12Mbps) peripheral controller that interfaces to…

Overview

The AL-USB2D-CTRL fully synthesizable core implements a complete high/full-speed (480Mbps/12Mbps) peripheral controller that interfaces to a UTMI USB port transceiver on one side and to a system’s microprocessor on the other. It is user-configurable for up to 15 IN and OUT endpoints, and includes power management and remote wake-up functions.

Options include a protocol aware DMA controller, support for a variety of widely used bus interfaces, and a UTMI Low Pin Interface (ULPI).

Designed for easy reuse in ASIC and FPGA implementations, the microcode-free design is strictly synchronous with positive-edge clocking, no internal tri-states and a synchronous reset; therefore scan insertion is straightforward. The core has been optimized and silicon proven on Xilinx and Altera FPGAs.

Options include a protocol aware DMA controller, support for a variety of widely used bus interfaces, and a UTMI Low Pin Interface (ULPI).

Designed for easy reuse in ASIC and FPGA implementations, the microcode-free design is strictly synchronous with positive-edge clocking, no internal tri-states and a synchronous reset; therefore scan insertion is straightforward. The core has been optimized and silicon proven on Xilinx and Altera FPGAs.

Key features

- USB 2.0 compliant device.

- ULPI/ UTMI interface to the external PHY

- 32bit Avalon or AHB slave interface to application.

- Supports high speed (480Mbps), full speed (12Mbps) bit rates.

- Supports Control, Bulk, Interrupt and Isochronous transfers.

- Remote wake-up function capable.

- Performs CRC check/generation.

- Performs PID verification, address recognition and handshake evaluation and response.

- Decodes and handles standard USB commands.

- Endpoints, their parameters and FIFO densities are configurable.

- Preconfigured for 3 endpoints (control, bulk in, bulk out)

- Software/ Hardware controlled enumeration.

- Compact plug-in solution for SOC applications.

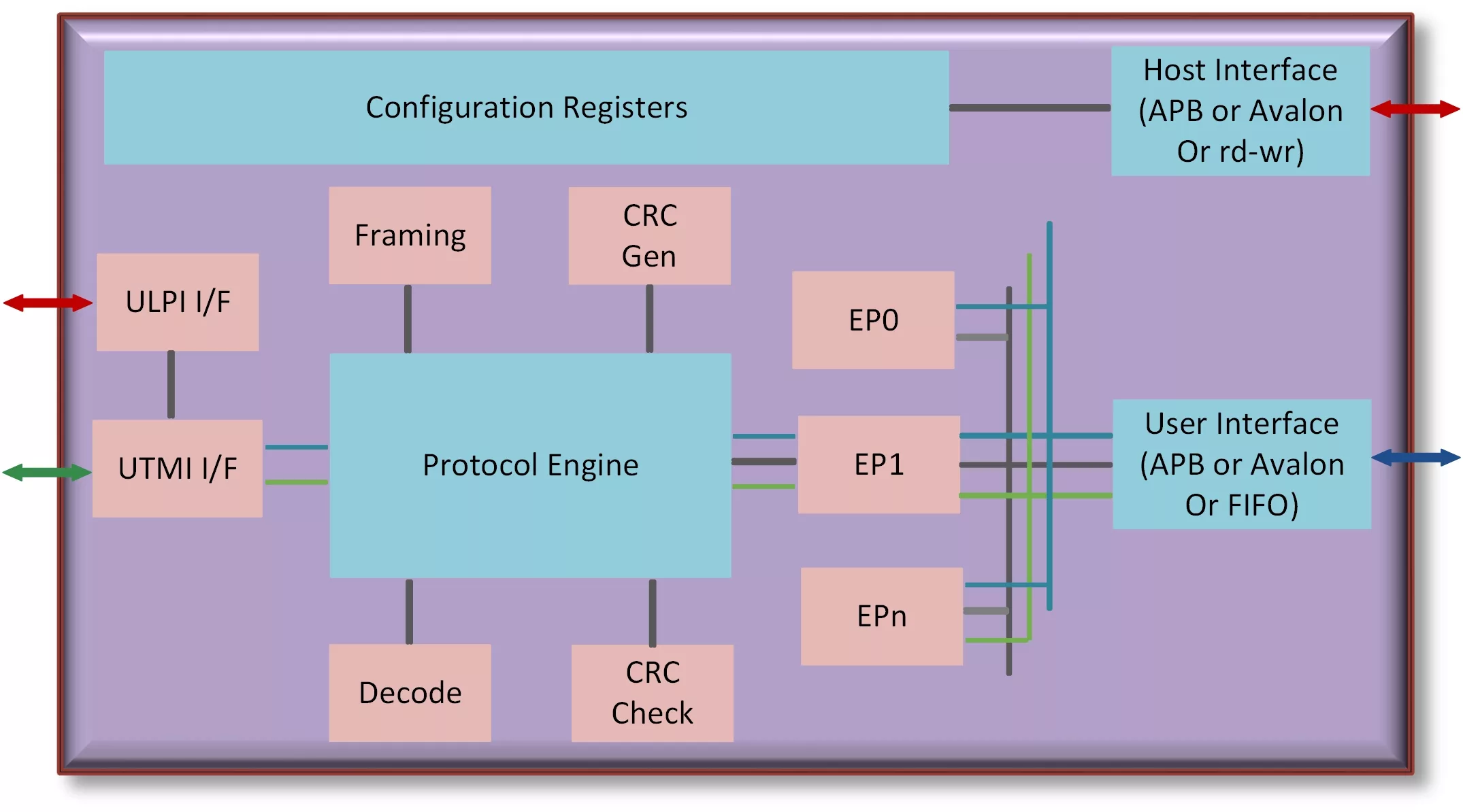

Block Diagram

AL-USB2D-CTRL block diagram

Specifications

Identity

Part Number

AL-USB2D-CTRL

Vendor

Atria Logic, Inc.

Type

Silicon IP

Files

Note: some files may require an NDA depending on provider policy.

Provider

Atria Logic, Inc.

HQ:

USA

Atria Logic is a leading provider of HW/SW FPGA and SoC IP cores and design engineering services, specializing in applications for medical imaging, multimedia, storage and networking. In addition, we also specialize in heterogeneous computing engineering services for computer vision applications in such applications as industrial automation, video surveillance and automotive.

Our IP core portfolio includes H.264 video encoders and decoders, H.264 players, DDR I/II/III and QDR IV Extreme Performance PHY and memory controllers, USB 2/3 controllers, PCIe Gen 1/2 PHYs, NVMe validation test suites, and Gb Ethernet MAC controllers. Our IP cores have been designed for ease of reuse and configurability to speed up SoC and FPGA implementations.

Our design services include IP customization, SoC integration, FPGA and SoC implementations, firmware development, software porting and optimization.

We are headquartered in Sunnyvale, California, USA, in the heart of Silicon Valley.

Technology Focus:

Video/Image processing

Heterogeneous Processing

High Power Computing

Computer Vision and Video Analytics

High speed memory controllers and Standard bus architectures

Network Processing

FPGA/ASIC/SoC design services

HW/SW domain consultancy and services

Business Domains

Medical Imaging

Video Surveillance

Industrial Automation

Enterprise and Datacenter Storage

Broadcast

Automotive Assisted Driver Assistance Systems

Learn more about USB IP core

Exploring USB Applications and the Impact of USB IP

Understanding USB IP and Its Role in SOC Integration

What Designers Need to Know About USB Low-Power States

In addition to performance and interoperability, achieving low power has been one of the requirements for industry standards specifications. Some of the key specifications like Universal Serial Bus (USB), PCI Express (PCIe), and MIPI have defined power saving features for burst traffic. This whitepaper explains how Synopsys USB IP offers low power using various low power states that go beyond the basic features.

New USB 80Gbps Specification Boosts Data Rate, Enables Four Protocols on One Bus

Gervais Fong, Synopsys

New USB Device Class Specification Broadens Use Cases for I3C and I3C Basic

Sharmion Kerley, MIPI Alliance

Frequently asked questions about USB IP cores

What is USB 2.0 CONTROLLER IP CORE?

USB 2.0 CONTROLLER IP CORE is a USB IP core from Atria Logic, Inc. listed on Semi IP Hub.

How should engineers evaluate this USB?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this USB IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.