MIPI SPP Synthesizable Transactor provides a smart way to verify the MIPI SPP component of a SOC or a ASIC in Emulator or FPGA platform. MIPI SPP Synthesizable Transactor provides an smart way to verify the MIPI SPP bi-directional two-wire bus. The SmartDV's MIPI SPP Synthesizable Transactor is fully compliant with Specification for SPP version 1.0 and provides the following features.

MIPI SPP Synthesizable Transactor

Overview

Key Features

- Compliant with MIPI SPP version 2.0 specification.

- Full MIPI Debug functionality.

- Supports all Debug CCC's and Opcodes

- Supports Error handling methods

- Action and Event indications and opcode related to JTAG in the sneakpeek pockets

- Supports below two different header structurs

- For high speed mode full sneakpeek

- For low band width TinnySPP(4Byte header derivative of SPP)

- Fully synthesizable

- Static synchronous design

- Positive edge clocking and no internal tri-states

- Scan test ready

- Simple interface allows easy connection to microprocessor/microcontroller devices

- Supports on-the-fly protocol and data checking

- Ability to transmit strings to help verification of SOC

- Notifies the test bench of significant events such as transactions, warnings,and protocol violations

- MIPI SPP Synthesizable VIP comes with complete test suite to verify each and every feature of MIPI SPP specification

- Status counters for various events in bus

Benefits

- Compatible with testbench writing using SmartDV's VIP

- All UVM sequences/testcases written with VIP can be reused

- Runs in every major emulators environment

- Runs in custom FPGA platforms

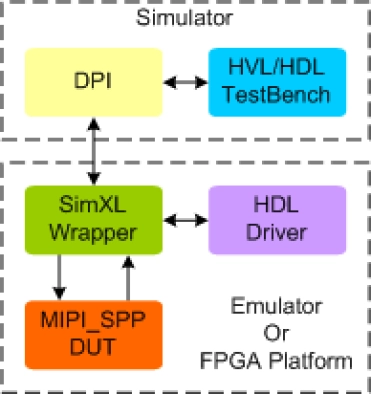

Block Diagram

Deliverables

- Synthesizable transactors

- Complete regression suite containing all the MIPI SPP testcases

- Examples showing how to connect various components, and usage of Synthesiable VIP

- Detailed documentation of all DPI, class, task and functions used in verification env

- Documentation contains User's Guide and Release notes