MIPI DEBUG Synthesizable Transactor provides a smart way to verify the MIPI DEBUG component of a SOC or a ASIC in Emulator or FPGA platform. MIPI DEBUG Synthesizable Transactor provides an smart way to verify the MIPI DEBUG bi-directional two-wire bus. The SmartDV's MIPI DEBUG Synthesizable Transactor is fully compliant with Specification for DEBUG version 1.0 and provides the following features.

MIPI DEBUG Synthesizable Transactor

Overview

Key Features

- Compliant with MIPI Debug version 1.0 specification.

- Full MIPI Debug functionality.

- Support full I3C Slave with CCC, Hot Join, IBI, DAA and HDR mode.

- Full Link and Network/Transport layer.

- Support Network adaptors for following

- SPP

- STP

- SAM

- TWP

- UART

- Supports upto 16 Network Adaptors

- Supports error detection and recovery

Benefits

- Compatible with testbench writing using SmartDV's VIP

- All UVM sequences/testcases written with VIP can be reused

- Runs in every major emulators environment

- Runs in custom FPGA platforms

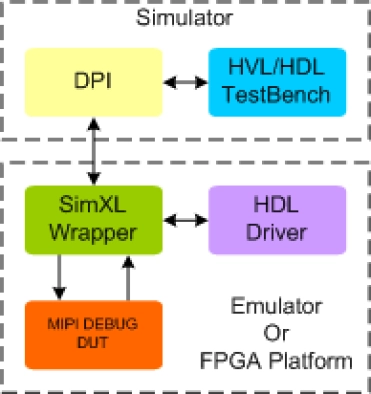

Block Diagram

Deliverables

- Synthesizable transactors

- Complete regression suite containing all the MIPI DEBUG testcases

- Examples showing how to connect various components, and usage of Synthesiable VIP

- Detailed documentation of all DPI, class, task and functions used in verification env

- Documentation contains User's Guide and Release notes