Overview

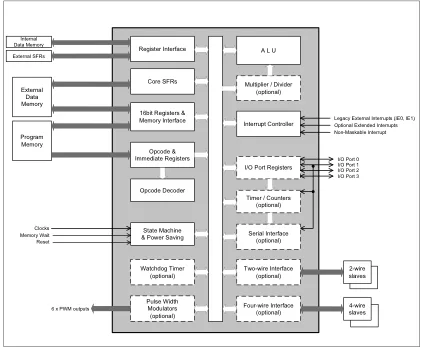

The M8051W V5.0 is a high performance core that executes each machine cycle in two clock cycles, giving a clock-for-clock performance that is six times faster than the M8051 and M8052 cores. They remain, however, binary and memory cycle compatible with Intel MCV-51 devices.

The M8051W incorporates various extended features, such as extra data pointers, support of extra interrupts and interrupt priority levels, optional multiple clock domains for optimising power consumption and support for synchronous memory cells.

The M8051W V5.0 includes many key enhancements and product updates when compared to the Mentor Graphics M8051W+ core offered by IP-Extreme. All product enhancements and support services of the M8051W V5.0 offered by Syntill8, as well as design services, are provided by the original M8051W IP architect.

Three additional peripheral cores that available for use with the M8051W include the M2WIS (a two-wire slave interface), the M4WIS (a four-wire slave interface) and the UDPMAC (a 1Gbps Ethernet MAC with an RGMII interface).

Learn more about MCU IP core

Daryl Khoo, Renesas

Eric Esteve

In this article, we’ll cover how modern software tools, hardware development ecosystems, and ready-made firmware stacks with code examples ease system design and development of 32-bit systems.

Don Dingee

This article describes ongoing internal project activities at eInfochips in the control systems domain for applications in motor and engine controls aimed for aerospace and automotive segments.

Don Dingee