JESD204A IP Core

Overview

JEDEC Standard No. 204A (JESD204A) describes a serialized interface between data converters and logic devices. It contains the information necessary to allow designers to implement devices which can communicate with other devices that are compliant with the standard. Lattice’s JESD204A IP Core offerings support both an Rx core (ADC to FPGA direction) and/or a Tx core (FPGA to DAC direction). The Rx and Tx cores can each be generated separately and with different parameters.

Key Features

- Compliant with JEDEC Standard No. 204A (JESD204A) April 2008

- Rx core performs lane alignment buffering / detection / monitoring and correction

- Rx core performs frame alignment detection / monitoring and octet reconstruction

- Rx core performs user-enabled descrambling

- Rx core recovers link configuration parameters during initial lane synchronization and compares them to userselected parameters to generate a configuration mismatch error

- Tx core performs user-enabled scrambling

- Tx core generates initial lane alignment sequence

- Tx core performs alignment character generation

- Tx core sources link configuration data with user selected parameter values during initial lane synchronization sequence

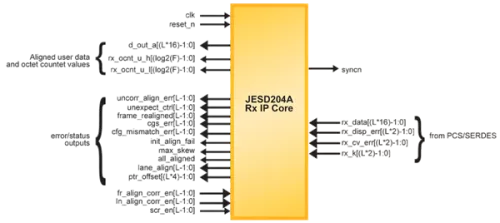

Block Diagram

Technical Specifications

Related IPs

- ColdFire V2 IP Core low-gate count, high performance ColdFire architecture

- MD5 IP Core Message Digest Function

- AES Encryption & Decryption IP Core − Single Configurable Block Cipher Mode

- GCM-AES IP Core − Authenticated Encryption & Decryption

- AES Encryption & Decryption IP Core − Programmable Block Cipher Modes

- 802.11i CCMP/TKIP IP Core