High-precision 16-bit complex digital down-converter / IQ demodulator with a fully configurable decimation filter stage. Ideal for the conversion of IF signals to baseband for subsequent processing.

Features a precision digital oscillator and a highly-optimized decimation filter section.

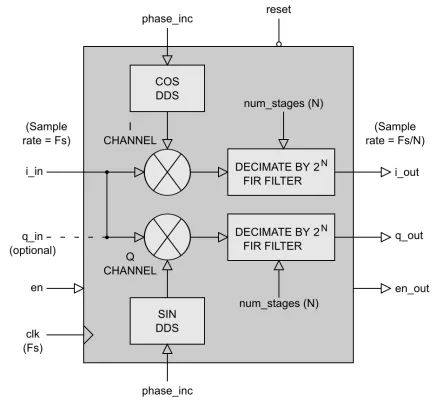

Complex Digital Down Converter

Overview

Key Features

- 16-bit signed complex (IQ) data samples

- Precision digital oscillator (> 100 dB SFDR)

- Decimation factors from 0 to 2^N

- Only 12 multipliers per decimate-by-2 stage

- 80 dB stop-band attenuation

- Typical FPGA sample rates of 250 MHz+

- Ideal for all digital modulation schemes

- Examples include: QPSK, QAM, WiMAX, WCDMA, COFDM etc.

Benefits

- Technology independent soft IP Core

- Suitable for FPGA, SoC and ASIC

- Supplied as human-readable source code

- One-time license fee with unlimited use

- Field tested and market proven

- Any custom modification on request

Block Diagram

Deliverables

- VHDL source-code (or Verilog on request)

- Simulation test bench

- Examples and scripts

- Full pdf datasheet

- One-to-one technical support

- One years warranty and maintenance

Technical Specifications

Short description

Complex Digital Down Converter

Vendor

Vendor Name

Foundry, Node

All

Availability

Immediate