The SDCRDAC24b is a 24-bit sigma-delta charge-redistribution digital-to-analog converter (DAC). It is designed to have high absolute accuracy, low flicker noise and low power consumption, and is robust against temperature variations and radiation. This makes the DAC ideally suited for demanding control applications in a wide variety of environments.

This IP is silicon proven.

24-Bit High resolution sigma-delta charge-redistribution DAC

Overview

Key Features

- SNR: 122dB (10μHz - 1Hz)

- SNR: 130dB (1Hz - 50Hz)

- Sample rate: 0-200kS/s

- Total out-of-band noise: < -60dB

- Quasi-differential output

- Low latency: 4.25μs

- Radiation hardened

- Total power consumption: 2.5mW

- Gain stability vs temperature: 1.5 ppm/K

- Design is scalable with regard to area and performance

- Technology: UMC 0.18μm CMOS

- Silicon proven

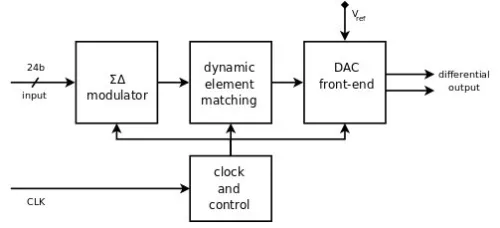

Block Diagram

Applications

- High-precision control systems

- Automatic test equipment

- Gain and offset adjustment/calibration

- Programmable voltage and current sources

- Process and servo control

- High-quality audio (with minor scaling and other modifications to DAC)

Technical Specifications

Foundry, Node

UMC 0.18μm CMOS

Maturity

Silicon proven

UMC

Silicon Proven:

180nm

Related IPs

- IBM 65nm 24bit Sigma-Delta DAC

- IBM 65nm 24-bit Stereo Sigma-Delta ADC

- SMIC 0.13um 24-Bit Stereo Sigma-Delta ADC

- SMIC 65nm 24Bit Sigma-Delta

- SMIC 65nm Low Leakage Process 24Bit Stereo Sigma-Delta ADC/DAC

- The S13V33_CODEC_04 integrates: 2-channel 24bit sigma-delta ADC and 2-channel 24bit sigma-delta DAC with headphone driver amplifier.