Alphawave provides a family of GFP-F IP blocks for all applications and size constraints ready for FPGA and ASIC solutions. The family covers single channel and multichannel options, full bandwidth and Interlaken interface options. Other sub-variants are available based on feature requirements.

The multi-channel GFP version can be seamlessly integrated with Alphawave MC ODUj to perform ODUFLEX(GPF-F) function for mapping packet clients.

The GFP-F IP encapsulates/decapsulates client data to/from Generic Framing Procedure (GFP-F) based on ITU G.7041 Rec. The multi-channel version also supports ITU G.7044 (ex G.HAO Hitless Adjustment ODUFLEX). The single channel version (SC_GFP-F) is targeted to compact and small footprint applications.

The MC_GFP-F can simultaneously support up to 8/32/80 independent channels for 10/40/100G applications respectively and is fully software configurable. A single Multi-channel GFP-F engine services the client data in a multiplexed fashion.

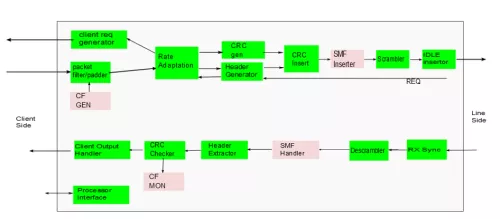

In the source direction, the MC_GFP-F wrapper encapsulates the client data frame/packet from each individual client channel with the ITU G.7041 GFP-F framing structure. The client data is sent to the GFP-F wrapper from the client input bus, where individual channels are multiplexed onto the input bus. The GFP framed client data is then sent to the line-side.

In the sink direction, the GFP-F wrapper decapsulates ITU G.7041 GFP-F frames from different channels (e.g. individual ODU channels) into client data. Similar to the source side, the input and output buses are multi-channel and time-multiplexed.

100G/40G/25G/10G GFP Mappers

Overview

Key Features

- Core Features

- • Fully compliant with G.7041 and G.7044 (ex G.HAO)

- • Configurable per channel GFP Header fields

- • Programmable per channel core header, payload header, and extension header single bit error correction

- • Programmable per channel payload frame check sequence (pFCS) insertion and processing assigned to value of client channel.

- • Extension header error control field is inserted and processed

- • Programmable per channel payload area scrambling

- • Input port allows per channel management frame generation

- • Received payload header values are captured in software readable registers

- • Flexible data-bus width for non-standard applications

- Key Features

- • Supports mapping of generic client packet data e.g. Ethernet, MPLS

- • Supports up to 10/40/100G transmission

- • Supports up to 8/32/80 channels for multi-channel version

- • Perfect solution for ODUflex(GFP-F) mapping of multiple client data channels onto multiple ODUflex signal streams onto ODU4/OPU4 using ODTU4.ts

- • Perfect solution for multi-channel ODUj

- • GFP IDLEs are optionally inserted to facilitate rate adaptation or when client data is not available

- • Programmable time multiplexing of multi-channels and programmable channel rate from 1.25Gbps to 100Gbps in 1.25Gbps increments

- • Easy “plug and play” setup!

- Optional Features

- • 10/40/100Gbps

- • Single channel or Multichannel support

- • Client side Interface is Interlaken or a generic interface for full bandwidth support

- • Line side interface connects seamlessly to Precise-ITC MC ODUj/MC FIFO Interface

- • 10G: 4 or 8 byte client and line side interfaces running at 315MHz and 155MHz respectively

- • 40G: 16 or 32 bytes client and line side interfaces running at 165MHz and 330MHz respectively

- • 100G: 40 or 64 bytes client and line side interfaces running at 350MHz and 220MHz respectively

- • Other bus widths available based on parameterization

- • Automatic 8, 12 or 64 byte Management Frame generation options

- • Optional S/W Generated Client Management frames and Management Communication frames.

- • Optional FCS error aligned with EOP

- • Optional processor i/f with 32-bit registers

- • Per channel Counters TX: frames sent, idle frames sent, client management frames sent

- • Per channel Counters RX: received frames, received idle frames, received client management frames, core header single-bit errors, core header multi-bit errors, payload header single-bit errors, payload FCS errors, extension header single-bit errors, extension header multi-bit errors

Block Diagram