Amidst a rich a-la-carte offering, shCODlp-100.02 is an optimized and complete configuration around high performance DAC and ADC cores which provide a higher SNR for the smallest silicon area.

Fabless companies targeting high fabrication volume would benefits from shCODlp-100.02 optimization for 0.11 um optically shrunk processes.

100 dB of SNR, 24-bit stereo audio CODEC with headphone driver and digital mixer

Overview

Key Features

- Maximized yield with the best trade-off between silicon area and SoC / PCB costs

- Capacitor-less headphone driver

- Filter-less line-out

- PLL-less feature to avoid jitter noise issues

- Single master clock generates all sampling frequencies

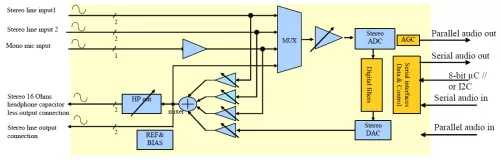

Block Diagram

Technical Specifications

Short description

100 dB of SNR, 24-bit stereo audio CODEC with headphone driver and digital mixer

Vendor

Vendor Name

Foundry, Node

TSMC 110nm GP

Maturity

In Production

TSMC

In Production:

110nm

G

,

110nm

HV

,

110nm

LVP

Related IPs

- Audio CODEC with 100 dB SNR, 24-bit stereo channels and cap-less headphone driver

- 100 dB of SNR, 24-bit stereo audio CODEC with 8 ADC paths, an embedded regulator and headphone/line-out driver

- 90 dB of SNR, 24-bit stereo audio CODEC with 450 mW mono speaker driver and headphone output

- 90 dB of SNR, 24-bit stereo audio CODEC with 450 mW mono speaker driver and headphone output

- 24-bit pure digital audio CODEC with 100 dB SNR stereo PDM-to-PCM and up to 110 dB SNR stereo PWM DAC with ASRC

- 90 dB of SNR, 24-bit mono audio ADC, stereo audio DAC with capless headphone driver