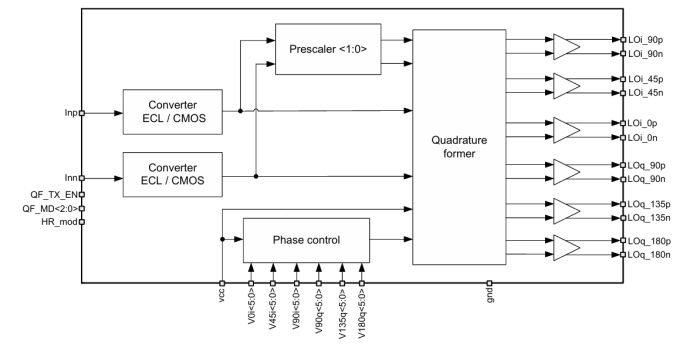

This device is designed to generate a quadrature local oscillator signal. A quadrature generator circuit constructed in CMOS logic and consists of two converters ECL/CMOS, quadrature former with input frequency divider by 2 or 4, prescaler by 2, 4, 8, 16 and phase control block, with ability of fine tuning of output signal phase. To reduce phase noise output triggers are strobbed by high-frequency signal.

0.075 - 3 GHz quadrature former

Overview

Key Features

- TSMC CMOS 65 nm

- Output frequency range 0.075-3 GHz

- Input frequency division (by 2, 4, 8, 16, 32 or 64)

- High accuracy of the phase control

- Output signal strobbing

Block Diagram

Applications

- Quadrature signal processing for mixer

Deliverables

- Schematic or NetList

- Abstract model (.lef and .lib files)

- Layout view (optional)

- Behavioral model (Verilog)

- Extracted view (optional)

- GDSII

- DRC, LVS, antenna report

- Test bench with saved configurations (optional)

- Documentation

Technical Specifications

Short description

0.075 - 3 GHz quadrature former

Vendor

Vendor Name

Foundry, Node

TSMC CMOS 65 nm

Maturity

silicon proven

Availability

Now

TSMC

Silicon Proven:

65nm

G