multi-die interLink IP

Filter

Compare

3

IP

from

3

vendors

(1

-

3)

-

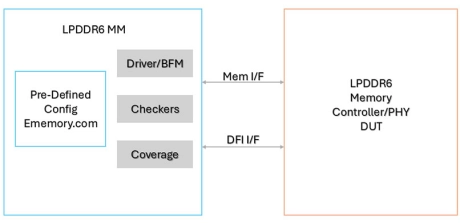

Simulation VIP for LPDDR6

- This Verification IP (VIP) is intended for modeling the upcoming JEDEC Low-Power Memory Device, LPDDR6 design specification.

- It provides a mature, highly capable compliance verification solution that supports simulation, formal analysis, and hardware acceleration platforms, making it applicable to intellectual property (IP), system-on-chip (SoC), and system-level verification.

-

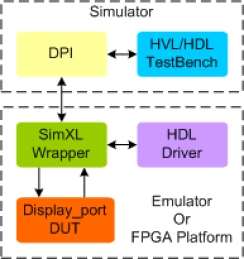

Verification IP for DisplayPort/eDP/DSC/DPI

- A comprehensive VIP solution for DisplayPort (DP) and eDP source and sink designs. DP VIP implements a complete set of models, protocol checkers and compliance testsuites in 100% native SystemVerilog and UVM .

- Comprehensive support for DP/eDP source and sink design verification.

-

Display Port Synthesizable Transactor

- Supports full Display port source device and sink device functionality

- Supports multi lanes upto 4 lanes

- Supports control symbols for framing(Both Default & Enhanced framing mode)

- Supports interlaced & non-interlaced video stream