memory controller with execute in place IP

Filter

Compare

12

IP

from

5

vendors

(1

-

10)

-

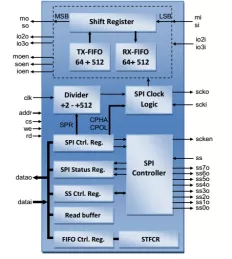

SPI FLASH Controller with Execute in place – XIP (SINGLE, DUAL and QUAD SPI Bus Controller with DDR / DTR support and optional AES Encryption)

- Set of software accessible control registers to execute any Flash memory command

- Supports any device clock frequency, polarity and phase,

- Programmable baud rate generator,

- Built in FLASH Commands decoder supports most popular FLASH devices,

-

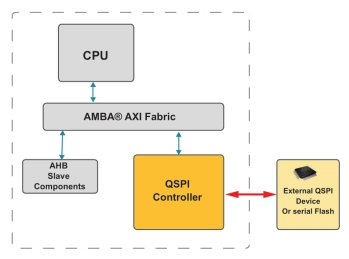

AXI Quad SPI Controller with Execute in Place (XIP)

- The Ultra High-Speed cache memory is an adaptable, independent, non-coherent cache Intellectual Property (IP) featuring an advanced cache architecture.

- This architecture enhances system performance, scalability, power efficiency, data locality, application responsiveness, cost optimization, and market competitiveness, providing a distinctive business value.

-

PSRAM Memory Controller IP

- DFSPI – SPI FLASH Controller with Execute in place – XIP (SINGLE, DUAL and QUAD SPI Bus Controller with DDR / DTR support and optional AES Encryption) + … NOR & NAND Flash Memory Support

-

HYPERBUS™ Memory Controller

- The HyperBus™ Memory Controller IP Core is a high-speed, fully configurable SPI master/slave solution, designed for seamless integration into modern SoC and FPGA architectures.

- Building on the proven DFSPI core, this IP bridges easily to APB, AHB, and AXI buses, supporting SINGLE, DUAL, QUAD, and OCTAL SPI modes for maximum design flexibility.

-

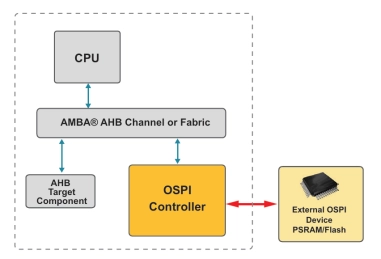

AHB Octal SPI Controller with PSRAM and XIP Support

- The Octal SPI Memory Controller IP core is a serial peripheral interface (SPI) master which controls an external serial device, usually an industry-standard FLASH or PSRAM memory device.

- In Software Mode, an AHB Master may access the register interface of the Controller to implement a wide range of protocol variants and/or commands on the SPI bus.

-

FSPI Controller – XIP functionality (SINGLE, DUAL, QUAD and OCTAL SPI Bus Controller with Double Data Rate support)

- Set of software accessible control registers to

- execute any Flash memory command

- Support for most popular SPI like FLASH memories and PSRAM

- Supports any device clock frequency, polarity and phase

-

QSPI FLASH Controller – XIP functionality (SINGLE, DUAL and QUAD SPI Bus Controller with Double Data Rate support)

- Set of software accessible control registers to execute any Flash memory command

- Supports any device clock frequency, polarity and phase,

- Programmable baud rate generator,

- Built in FLASH Commands decoder supports most popular FLASH devices,

-

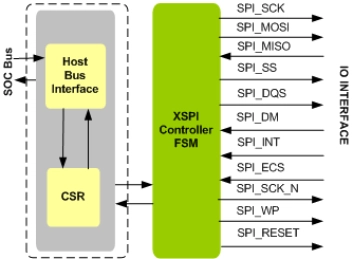

XSPI Controller IIP

- Compliant with XSPI protocol of JEDEC standard version 1.0 specification

- Support single master and multiple slaves per interface port

- Support source synchronous clocking

- Support Deep power down enter and exit commands

-

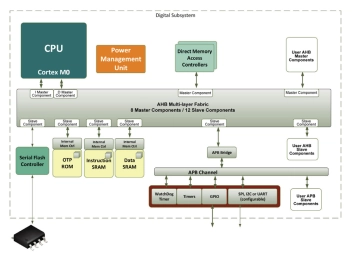

AHB Performance Subsystem - ARM Cortex M0

- The AHB Performance Subsystem is an AMBA® based system that is useful as the digital infrastructure for building low power SOCs needing additional performance.

- This AHB Multi-matrix system contains a flexible Power Management Unit for controlling power sequencing of the CPU and peripherals.

- The PMU can easily be extended to control additional cores, peripherals and even analog subsystems on the same SOC

-

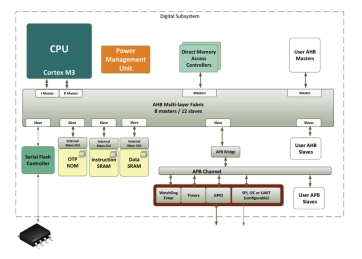

AHB Performance Subsystem - ARM Cortex M3

- The AHB Performance Subsystem is an AMBA® based system that is useful as the digital infrastructure for building low power SOCs needing additional performance.

- This AHB Multi-matrix system contains a flexible Power Management Unit for controlling power sequencing of the CPU and peripherals.

- The PMU can easily be extended to control additional cores, peripherals and even analog subsystems on the same SOC.