automotive RISC-V processor IP

Filter

Compare

17

IP

from

11

vendors

(1

-

10)

-

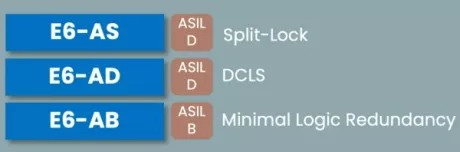

32-bit RISC-V processor specifically designed for the Automotive and Functional Safety markets

- 32-bit RISC-V ISA

- ASIL B and ASIL D area optimised product variants

- Functional Safety Package and Independent Assessment

-

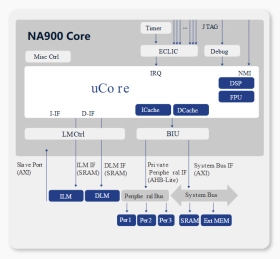

32-Bit Automotive Processor - 9-Stage Pipeline, Dual-issue

- NA900 series processor is the 1st ISO26262 ASIL-B/D Product Certified RISC-V CPU IP, Nuclei self-developed STL supports multiple ASIL-B automotive use cases.

-

32-Bit Automotive Processor - 3-Stage Pipeline, Single/Dual-issue

- NA300 series processor is a ISO26262 ASIL-B/D Certified RISC-V CPU IP,Nuclei self-developed STL supports multiple ASIL-B automotive use cases.

-

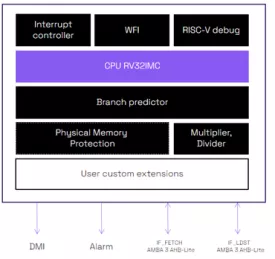

32-bit RISC-V embedded processor with TÜV SÜD ISO 26262 ASIL B certification

- Flexible use cases

- roven technology

- State-of-the-art safety and security

-

8-stage superscalar processor that supports ISO 26262 ASIL (Automotive Safety Integrity Level) -D level functional safety for automotive applications

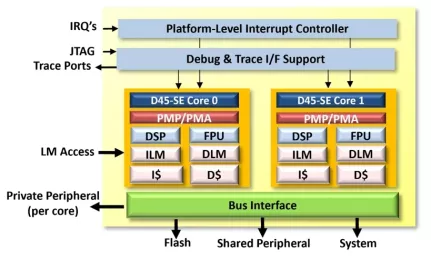

- The 32-bit D45-SE is an 8-stage superscalar processor that supports ISO 26262 ASIL (Automotive Safety Integrity Level) -D level functional safety for automotive applications.

-

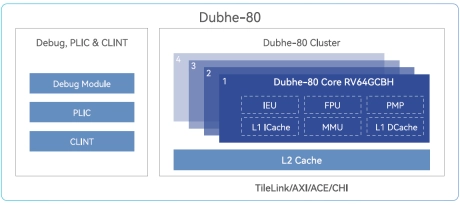

64-bit application processor for energy-efficient computation

- Dubhe-80 processor features a 9+ stage, 3-issue, out-of-order pipeline, fully compliant with a rich set of RISC-V extensions of RV64GCBH_Zicond_Zicbom_Zicboz_Zicbop.

- With a score of 8.5 SPECInt2006/GHz, Dubhe-80 is designed for mobile, desktop, AI, and automotive applications that require highly energy-efficient computation.

-

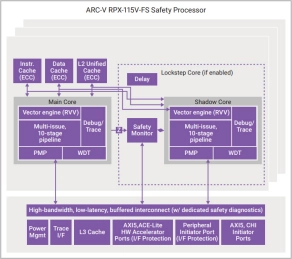

ARC-V RPX Series Functional Safety Processor IP

- The ARC-V™ RPX-110 series functional safety (FS) processors, which include the RPX-110-FS, RPX-115-FS, RPX-110V-FS, and RPX-115V-FS processors simplify development of high-performance safety-critical applications and accelerate ISO 26262 certification for automotive system-on-chips (SoCs).

- The Automotive Safety Integrity Level (ASIL) D compliant processors feature a pre-verified dual-core lockstep implementation including an integrated safety monitor.

- Additionally, they offer the flexibility to operate in an independent “hybrid” mode for ASIL B or non-automotive applications that demand higher performance from the same design.

-

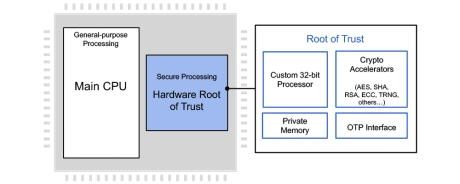

Embedded Hardware Security Module (Root of Trust) - Automotive Grade ISO 26262 ASIL-B

- The RT-64x Embedded Hardware Security Module (Root of Trust) family are fully programmable, ISO 26262 ASIL-B hardware security cores offering security by design for automotive applications.

- They protect against a wide range of failures such as permanent, transient and latent faults and hardware and software attacks with state-of-the-art anti-tamper and security techniques.

-

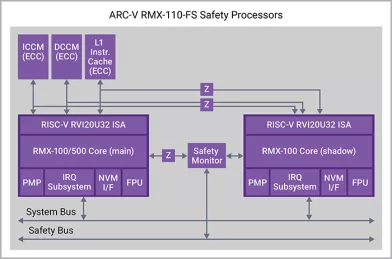

ARC-V RMX Series Functional Safety Processor IP

- Developed for full ASIL D compliance (systematic and random faults)

- Tightly-coupled dual-core safety implementation based on ultra-compact ARC-V RMX processors

- Single solution support for safety level up to ASIL D; Supports both ASIL D lockstep operation or ASIL B single-core operation (RMX-510-FS only)

- Integrated hardware safety features including ECC, user-programmable windowed watchdog timer, end-to-end protection (E2E) for buses/data-path, and lockstep safety monitor

-

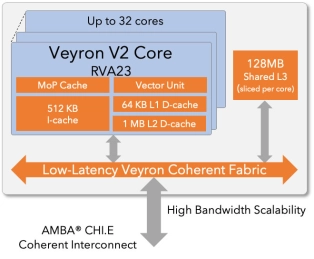

High-performance RISC-V CPU

- Fully compliant with the RVA23 RISC-V specification

- Comparable PPA to Arm Neoverse V3 / Cortex-X4

- Standard AMBA CHI.E coherent interface for SoC and chiplet integration

- Co-architected with Veyron E2 for seamless vector, AI acceleration, and big-little style heterogeneous compute configurations