USB Audio Device Class 3.0 IP

Filter

Compare

16

IP

from

7

vendors

(1

-

10)

-

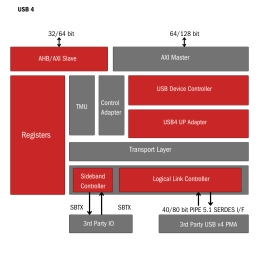

USB 4.0 - Enables fast data transfer, efficient power delivery, and connectivity

- USB 4.0 is the third major revision of the USB standard, offering data transfer speeds up to 20 Gbps via dual-lane operation. It supports multiple transfer modes and improved bandwidth utilization for high-speed applications.

- USB 4.0 enables seamless connectivity across various devices, from storage and printers to high-performance audio and video equipment. It enhances power delivery and ensures efficient data transfer for consumer electronics, networking, and industrial applications.

-

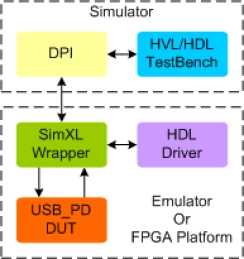

USB PD Synthesizable Transactor

- USB PD Features

- Supports USB Power Delivery Specification 3.1,3.0, 2.0 and 1.0

- Supports USB Type-C Cable and Connector Specification

- Supports Cable plug communication

-

USB 2.0 femtoPHY in GF (28nm, 22nm, 12nm)

- Complete mixed-signal physical layer for single-chip USB 2.0 Host, Device, and Dual Role applications Small PHY macro area: as small as 0.20 mm2

- Low power: as low as 50mW (during high-speed packet transmission)

- Advanced power management features including support for power supply gating, supply scaling, ultra-low standby current support, and power management unit (PMU) interrupt support

- Supports USB 2.0 ID-pin detection and OTG Voltage Detectors

-

USB 2.0 femtoPHY in GF (22nm) for Automotive Grade 1

- Complete mixed-signal physical layer for single-chip USB 2.0 Host, Device, and Dual Role applications Small PHY macro area: as small as 0.20 mm2

- Low power: as low as 50mW (during high-speed packet transmission)

- Advanced power management features including support for power supply gating, supply scaling, ultra-low standby current support, and power management unit (PMU) interrupt support

- Supports USB 2.0 ID-pin detection and OTG Voltage Detectors

-

USB 2.0 femtoPHY in TSMC (16nm, N7) for Automotive

- Complete mixed-signal physical layer for single-chip USB 2.0 Host, Device, and Dual Role applications Small PHY macro area: as small as 0.20 mm2

- Low power: as low as 50mW (during high-speed packet transmission)

- Advanced power management features including support for power supply gating, supply scaling, ultra-low standby current support, and power management unit (PMU) interrupt support

- Supports USB 2.0 ID-pin detection and OTG Voltage Detectors

-

USB 2.0 femtoPHY in Samsung (14nm, 11nm, 8nm, 7nm, 5nm, SF4X)

- Designed for advanced 1.8V CMOS planar bulk and FinFET process nodes

-

USB 2.0 femtoPHY in TSMC (40nm, 28nm, 22nm, 16nm, 12nm, 10nm, N7, N6, N5, N3P)

- Complete mixed-signal physical layer for single-chip USB 2.0 Host, Device, and Dual Role applications Small PHY macro area: as small as 0.20 mm2

- Low power: as low as 50mW (during high-speed packet transmission)

- Advanced power management features including support for power supply gating, supply scaling, ultra-low standby current support, and power management unit (PMU) interrupt support

- Supports USB 2.0 ID-pin detection and OTG Voltage Detectors

-

USB 2.0 femtoPHY in UMC (28nm, 22nm)

- Complete mixed-signal physical layer for single-chip USB 2.0 Host, Device, and Dual Role applications Small PHY macro area: as small as 0.20 mm2

- Low power: as low as 50mW (during high-speed packet transmission)

- Advanced power management features including support for power supply gating, supply scaling, ultra-low standby current support, and power management unit (PMU) interrupt support

- Supports USB 2.0 ID-pin detection and OTG Voltage Detectors

-

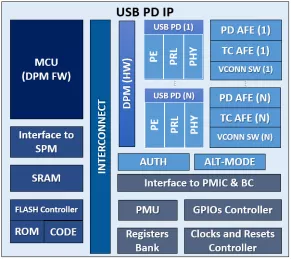

Fully Self-contained Single/Multi Port USB Type-C Power Delivery IP

- Fully compliant with USB PD Specification revision 3.0 and Type-C Cable and Connector specification revision 1.2

-

USB 2.0 femtoPHY in SMIC (40nm, 28nm)

- Complete mixed-signal physical layer for single-chip USB 2.0 Host, Device, and Dual Role applications Small PHY macro area: as small as 0.20 mm2

- Low power: as low as 50mW (during high-speed packet transmission)

- Advanced power management features including support for power supply gating, supply scaling, ultra-low standby current support, and power management unit (PMU) interrupt support

- Supports USB 2.0 ID-pin detection and OTG Voltage Detectors