RISC-V AI IP

Filter

Compare

65

IP

from

27

vendors

(1

-

10)

-

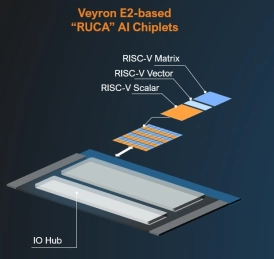

RISC-V AI Acceleration Platform - Scalable, standards-aligned soft chiplet IP

- Built on RISC-V and delivered as soft chiplet IP, the Veyron E2X provides scalable, standards-based AI acceleration that customers can integrate and customize freely.

-

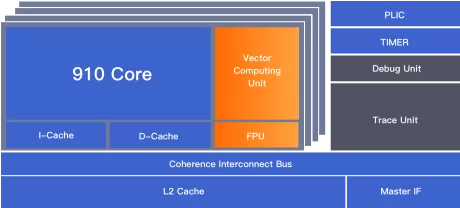

High-performance 64-bit RISC-V architecture multi-core processor with AI vector acceleration engine

- Instruction set: RISC-V RV64GC/RV 64GCV;

- Multi-core: Isomorphic multi-core with 1 to 4 optional clusters. Each cluster can have 1 to 4 optional cores;

-

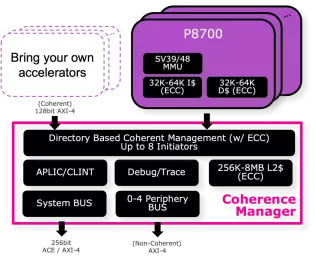

Data Movement Engine - Best in class multi-core high-performance AI-enabled RISC-V Automotive CPU for ADAS, AVs and SDVs

- The only Multi-Threaded Out-of-Order RISC-V Core with ASIL-B Certification

- Highly scalable multi-core, multi-cluster, coherent computing solution

- MIPS extensions for improved performance and functionality

- Use in Automotive, Datacenter, and Embedded applications

-

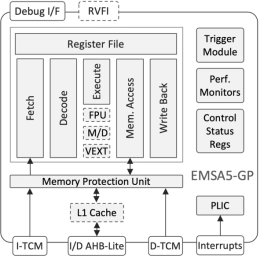

Vector-Capable Embedded RISC-V Processor

- The EMSA5-GP is a highly-featured 32-bit RISC-V embedded processor IP core optimized for processing-demanding applications.

- It is equipped with floating-point and vector-processing units, cache memories, and is suitable for concurrent execution in a multi-processor environment.

-

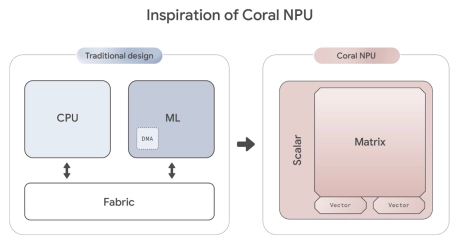

RISC-V-Based, Open Source AI Accelerator for the Edge

- Coral NPU is a machine learning (ML) accelerator core designed for energy-efficient AI at the edge.

- Based on the open hardware RISC-V ISA, it is available as validated open source IP, for commercial silicon integration.

-

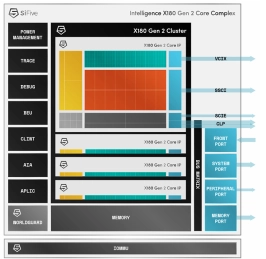

Multi-core capable 64-bit RISC-V CPU with vector extensions

- The SiFive® Intelligence™ X180 core IP products are designed to meet the increasing requirements of embedded IoT and AI at the far edge.

- With this 64-bit version, X100 series IP delivers higher performance and better integration with larger memory systems.

-

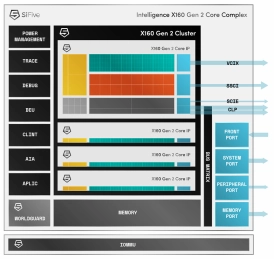

Multi-core capable 32-bit RISC-V CPU with vector extensions

- The SiFive® Intelligence™ X160 core IP products are designed to meet the increasing requirements of embedded IoT and AI at the far edge.

- With this 32-bit version, X100 series IP can be optimized for power efficiency and severely area-constrained applications.

-

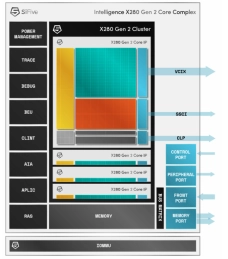

Multi-core capable RISC-V processor with vector extensions

- The SiFive® Intelligence™ X280 Gen 2 is an 8-stage dual issue, in-order, superscalar design with wide vector processing (512 bit VLEN/256-bit DLEN).

- It supports RISC-V Vectors v1.0 (RVV 1.0) and SiFive Intelligence Extensions to accelerate critical AI/ML operations.

-

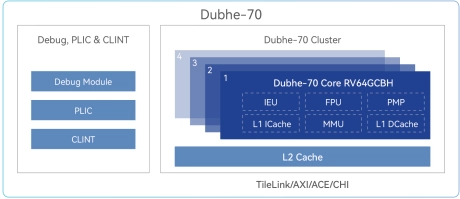

Ultra-low power consumption out-of-order commercial-grade 64-bit RISC-V CPU IP

- Dubhe-70 is a 9+ stage, 3-issue, out-of-order CPU IP that supports the rich RISC-V instruction set, RV64GCBH_Zicond_Zicbom_Zicboz_Zicbop.

- With a score of 7.2 SPECInt2006/GHz, Dubhe-70 targets applications that require highly energy-efficient computation, including mobile, desktop, AI, and automotive.

-

AI DSA Processor - 9-Stage Pipeline, Dual-issue

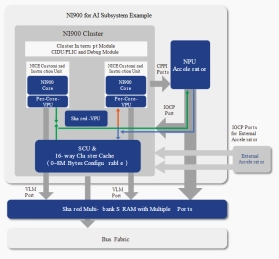

- NI900 is a DSA processor based on 900 Series.

- NI900 is optimized with features specifically targeting AI applications.