PCIe for USB4 IP

Filter

Compare

17

IP

from

7

vendors

(1

-

10)

-

PCIe Controller for USB4 with AXI

- Internal data path size automatically scales up or down (64-, 256-, 512- bits) based on link max. speed and width for reduced gate count and optimal throughput

- Configurable pipelining enables full speed operation on Intel and Xilinx FPGA, full support for production FPGA designs up to Gen4 x8/Gen3 x16 with same RTL code – Gen5 support pending

- Stringent implementation of PCIe to AXI Ordering Rules and AXI to PCIe Ordering Rules guarantees AXI deadlock prevention

- Carefully engineered AXI bridge & AXI interconnect allows full performance on AXI interfaces

-

PCIe Controller for USB4

- Internal data path size automatically scales up or down (256-, 512- bits) based on max. link speed and width for reduced gate count and optimal throughput

- Dynamically adjustable application layer frequency down to 8Mhz for increased power savings

- Optional MSI/MSI-X register remapping to memory for reduced gate count when SR-IOV is implemented

- Configurable pipelining enables full speed operation on Intel and Xilinx FPGA, full support for production FPGA designs (when supported)

- Ultra-low Transmit and Receive latency (excl. PHY)

-

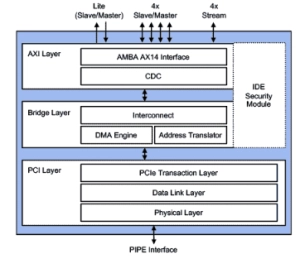

PCIe Controller for USB4 supporting up to PCIe 4.0 with AMBA interface

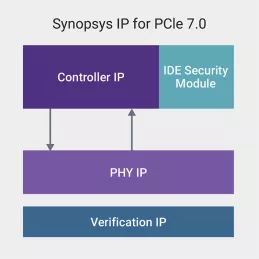

- Supports all required features of the PCI Express 5.0 (32 GT/s), 4.0 (16 GT/s), 3.1 (8 GT/s), 2.1 (5 GT/s), 1.1 (2.5 GT/s) and PIPE (8-, 16- and 32-bit) specifications

- Production-proven datapath support for 32b, 64b, 128b, 256b and 512b implementations

- Fully compliant with the PCI-SIG Single-Root I/O Virtualization (SRIOV) specification

- Application interfaces include the Synopsys native interface or the optional ARM® AMBA® 4 AXI and 3 AXI application interface (AMBA not available for Switch configurations)

-

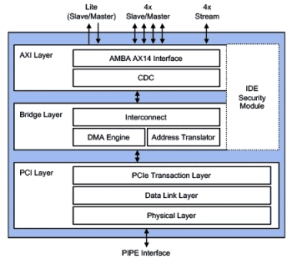

PCIe Controller for USB4 supporting up to PCIe 4.0

- Supports all required features of the PCI Express 5.0 (32 GT/s), 4.0 (16 GT/s), 3.1 (8 GT/s), 2.1 (5 GT/s), 1.1 (2.5 GT/s) and PIPE (8-, 16- and 32-bit) specifications

- Production-proven datapath support for 32b, 64b, 128b, 256b and 512b implementations

- Fully compliant with the PCI-SIG Single-Root I/O Virtualization (SRIOV) specification

- Application interfaces include the Synopsys native interface or the optional ARM® AMBA® 4 AXI and 3 AXI application interface (AMBA not available for Switch configurations)

-

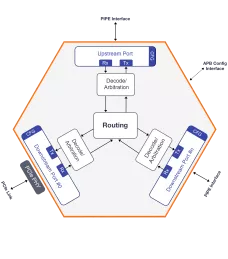

PCIe Switch for USB4

- Fully transparent design eliminates the need for Host configuration and management software

- Built-in support for PIPE-attached embedded endpoints (including 64-bit PIPE) for reduced BoM, latency, and power

- Seamless implementation on ASIC and FPGA with same RTL code base, up to x8 Gen4 per port on FPGA (or x16 Gen3)

- Lowest latency switching logic on the market (2 clock cycles)

-

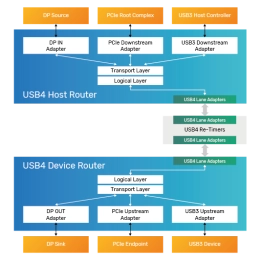

Simulation VIP for USB4

- Logical Layer

- Sideband channel

- Logical Layer State Machine

- GEN2, GEN3, and GEN4 speeds

-

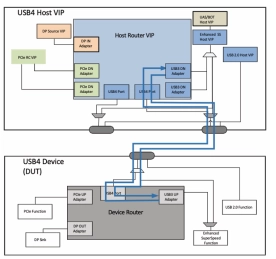

Verification IP for USB

- Avery VIP for USB is a comprehensive solution for verification of USB-based designs ranging from the USB 2.0, 3.x, and 4.0 standards, including xHCI host controllers and USB mass storage class standards for UAS and BOT.

- USB VIP allows users to verify their designs by developing custom tests at several levels of abstraction.

-

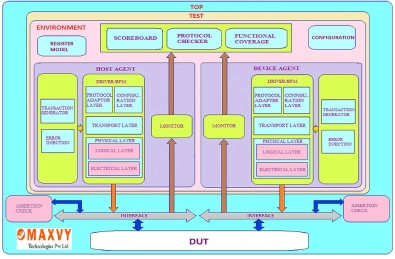

USB4 VIP

- The USB4 Verification IP (MX_USB4_VIP) provides a highly capable verification solution for the USB4 protocol which incorporating bus functional model (BFM), integrated protocol checkers and functional coverage along with assertion check

- The USB4 VIP can be readily customized and optimized for a wide range of specific system application

-

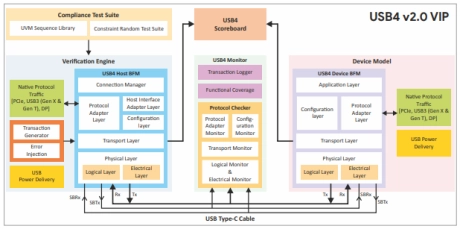

USB4 v2.0 Verification IP

- Fully compliant with USB4 specification v2.0 (October 2022) and Connection Manager version 2.0.

- Supports USB3.2 Specification, Revision 1.1 and backward compatibility to USB2.0.

- Supports USB Power Delivery Release 3.1, Version 1.8 and Type-C v2.2.

- Supports Thunderbolt (TBT3) interoperability.

-

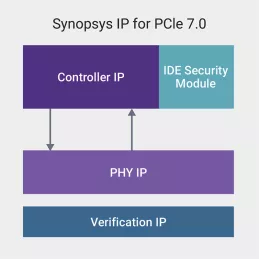

PCIe Switch Verification IP

- Compliant with the PCIe 6,5,4,3 specification.

- Support Pipe Specification 6.1.1

- NVMe on top of Low Power, CXS, CPI, CXL, CXL Security, PCIe Gen6/5/4/3 management

- Supports Pipe Specification 6.1 with both Low Pin Count and Serdes Architecture.