PCIe DMA IP

Filter

Compare

64

IP

from

25

vendors

(1

-

10)

-

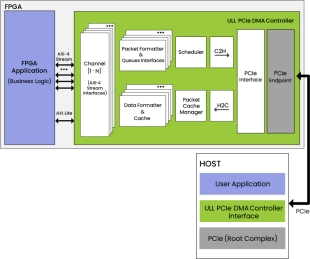

ULL PCIe DMA Controller

- The ULL PCIe DMA Controller is a high-performance, bidirectional data transfer solution. It is designed for seamless communication between FPGAs and host CPUs over PCIe.

- With a round-trip time as low as 585ns*, this IP core empowers developers to maximize resource utilization and achieve ultra-low latency without compromising performance.

-

PCIe DMA Controller (Low Latency)

- Implements standard Transaction layer functions e.g. TLP generation/reception, TLP completion handling and interrupt generation

- Implements 32-bit, 64-bit, 128-bit and 256-bit User application. (Width selection is based on PCIe endpoint interface width)

- PCIe Gen1, Gen2 and Gen3 support.

- Up to 8 independent DMA channels with each channel capable of operating in Block-DMA or Scatter-Gather DMA modes

-

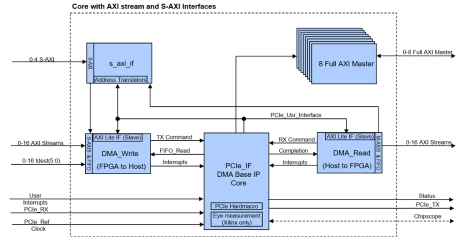

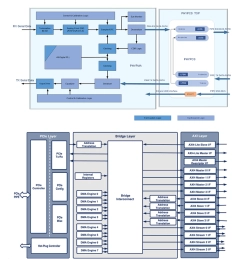

AXI Bridge with DMA for PCIe IP Core

- The AXI Bridge with DMA IP core is the ultimate PCIe DMA IP solution with a powerful mix of multiple industry standard AXI Interfaces.

- AXI Stream interfaces allow continuous data streaming from FPGA to Host or from Host to FPGA. S-AXI Memory mapped interfaces allow easy data access of remote memories in order to realize shared memory access or per to peer applications.

-

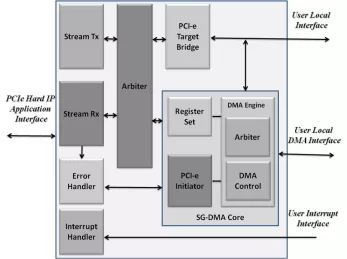

DMA Core for PCIe Hard IP

- TLP Encoding and Decoding

- Completion packet handling done by target bridge

- Integrated Arbiter with round robin fashion

- 32/64 bit AXI stream user interface from PCIe Hard IP depends on no. of PCIe lanes

-

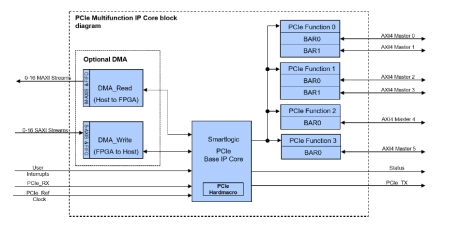

PCIe Multi-Function Option for DMA IP Cores

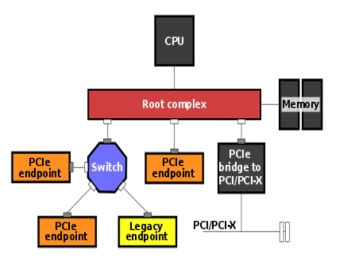

- The PCI Express specification allows endpoints that incorporate several physical PCIe functions that share the same PCIe connection. Such endpoints are called multi-function devices.

- The big advantage of a multi-function device is, that a separate device driver can be associated to each physical function.

- This simplifies driver development and maintenance significantly by separating the peripheral functions logically into different device drivers.

-

DMA for PCI Express (PCIe) Subsystem

- DMA for PCI Express Subsystem connects to the PCI Express Integrated Block. Both IPs are required to build the PCI Express DMA solution

- Support for 64, 128, 256, 512-bit datapath for UltraScale+™, UltraScale™ devices. Support for 64 and 128-bit datapath for Virtex®-7 XT devices

- Up to 4 host-to-card (H2C/Read) data channels for UltraScale+, UltraScale devices. Up to 2 such channels for Virtex-7 XT devices

- Up to 4 card-to-host (C2H/Write) data channels for UltraScale+, UltraScale devices. Up to 2 such channels for Virtex-7 XT devices

-

PCIe 1.1 Controller supporting Root Port, Endpoint, Dual-mode Configurations, with Built-in DMA and Configurable AMBA AXI Interconnect

- PCIe Interface

- Supported silicon:

- AMBA AXI Interface

- Data Engine and Address translation for PCIe-to-AXI and AXI-to-PCIe transfers

-

PCIe PHY and controller solution

- Brite 16Gbps PCIe PHY and controller solution provide high efficient interconnection that is optimized for PPA performance. The System can support short-reach or long-reach channels for plenty application scenarios.

- Brite PCIe controller to AXI architecture provides a high-performance, easy-to-use interconnect solution between PCI Express and the latest version of the AXI protocol. It inherits the leading architecture and features an AXI user interface with built-in DMA, compliant with the AMBA® AXI3 and AXI4 specifications.

-

PCIe - PCI Express Controller

- The PCIe 3.0 (Peripheral Component Interconnect Express 3.0) is a computer hardware interface standard that is used to connect various components to a computer's motherboard.

- It is the third generation of the PCIe standard and offers increased bandwidth, improved performance, and reduced power consumption compared to its predecessor, PCIe 2.0 Overall, PCIe 3.0 provides faster and more efficient communication between the various components in a computer, including graphics cards, network adapters, and storage devices, resulting in better overall performance.

-

R-Tile PCIe Hard IP

- R-Tile is a FPGA companion tile that supports configurations up to PCIe 5.0 x16 in Endpoint (EP), Root Port (RP), and Transaction Layer (TL) Bypass modes

- PCIe 3.0, 4.0, and 5.0 configurations are natively supported

- R-Tile also supports up to 16 SerDes channels through a PHY Interface for PCIe (PIPE) 5.1.1 in SerDes Architecture mode.